# Phase-change random access memory: A scalable technology

S. Raoux G. W. Burr M. J. Breitwisch C. T. Rettner Y.-C. Chen R. M. Shelby M. Salinga D. Krebs S.-H. Chen H.-L. Lung C. H. Lam

Nonvolatile RAM using resistance contrast in phase-change materials [or phase-change RAM (PCRAM)] is a promising technology for future storage-class memory. However, such a technology can succeed only if it can scale smaller in size, given the increasingly tiny memory cells that are projected for future technology nodes (i.e., generations). We first discuss the critical aspects that may affect the scaling of PCRAM, including materials properties, power consumption during programming and read operations, thermal cross-talk between memory cells, and failure mechanisms. We then discuss experiments that directly address the scaling properties of the phase-change materials themselves, including studies of phase transitions in both nanoparticles and ultrathin films as a function of particle size and film thickness. This work in materials directly motivated the successful creation of a series of prototype PCRAM devices, which have been fabricated and tested at phase-change material cross-sections with extremely small dimensions as low as 3 nm imes 20 nm. These device measurements provide a clear demonstration of the excellent scaling potential offered by this technology, and they are also consistent with the scaling behavior predicted by extensive device simulations. Finally, we discuss issues of device integration and cell design, manufacturability, and reliability.

### Introduction

Phase-change materials possess a unique combination of properties that make them promising candidates for the memory material in phase-change RAM (PCRAM) devices. A phase-change material is one that exists in at least two phases with remarkably different properties and can be repeatedly and rapidly cycled between these phases. The amorphous phase is characterized by a low optical reflectivity and high electrical resistivity, while the crystalline phase (or phases) shows high reflectivity and low resistivity. Although the change in reflectivity can be as great as approximately 30%, the change in resistivity can be as large as five orders of magnitude (a 10,000,000% difference).

Even though the principle of applying phase-change materials in a PCRAM cell was demonstrated as long ago as the 1960s [1], the technology has only recently been

developed seriously by a number of companies, and first products are about to enter the market. This renewed interest in PCRAM technology was triggered by the discovery of fast crystallizing materials such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) or Ag- and In-doped Sb<sub>2</sub>Te (AIST) [2, 3]. These materials can crystallize in less than 100 ns, as opposed to the materials used for early PCRAM demonstrations such as Te<sub>48</sub>As<sub>30</sub>Si<sub>12</sub>Ge<sub>10</sub>, which could require 10  $\mu$ s or more to crystallize [1]. These newer alloys switch faster because the crystallization process generates very little atomic motion [4], compared to the phase segregation that occurs in the earlier Te-rich alloys [5].

In PCRAM, the phase-change material is crystallized by heating it above its crystallization temperature (SET operation), and it is melt-quenched to make the material amorphous (RESET operation). These operations are controlled by electrical current: high-power pulses for the

©Copyright 2008 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied by any means or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

0018-8646/08/\$5.00 © 2008 IBM

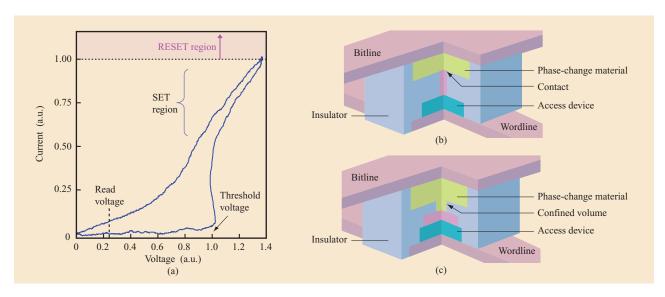

Phase-change device. (a) Typical current–voltage (*I–V*) curve for a phase-change device, demonstrating the threshold switching and differing amount of electrical power required for SET and RESET operation (a.u.: arbitrary unit). (b) A typical contact-minimized cell, the mushroom cell, forces current to pass through a small aperture formed by the intersection of one electrode and the phase-change material. (c) A typical volume-minimized cell, the pore cell, confines the volume of the phase-change material in order to create a small cross-section within the PCRAM device. (Republished from Reference [6]; ©2006 IEEE.)

RESET operation that places the memory cell into the high-resistance RESET state, moderate power but longer duration pulses for the SET pulse returning the cell to the low-resistance SET state, and finally very low power for retrieving data by sensing the device resistance [Figure 1(a)]. Other aspects of Figure 1 are discussed later in this paper.

A critical property of phase-change materials is the threshold switching [7–9]. Without this effect, PCRAM would simply not be a feasible technology, because in the high-resistance state, extremely high voltages would be required to deliver enough power to the cell to heat it above the crystallization temperature. However, when a voltage above a particular threshold  $V_t$  is applied to a phase-change material in the amorphous phase, the resulting large electrical fields greatly increase the electrical conductivity. This effect is still not completely understood but is attributed to the interplay between impact ionization and carrier recombination [7]. With the previously resistive material now suddenly highly conducting, a large current flows, which can then heat the material. However, if the current pulse is switched off immediately after the threshold switching, the material returns to the highly resistive amorphous phase after about 30 ns [10], with both the original threshold voltage  $V_{\rm t}$  and RESET resistance recovering slowly over time [10, 11]. If a current sufficient to heat the material above the crystallization temperature but below the melting

point is sustained for a sufficiently long time, the cell switches to the crystalline state [Figure 1(a)].

In this paper, we discuss the size-scaling aspects of phase-change memory. PCRAM technology seems to be a promising technology with respect to such scaling.

# Scaling of phase-change memory

The history of the solid-state memory industry and the semiconductor industry as a whole can be thought of as an incessant march along Moore's Law to smaller device dimensions enabling ever-increasing system functionality. In the case of memory, increased system functionality is manifested in the form of more megabytes (and now more gigabytes) in the same package size. Throughout this extensive history, extrapolation from the recent past has proven to be amazingly reliable for predicting near-future developments. Thus, the memory products that will be built in the next several years have long been forecast [12].

Beyond the near future, however, while the *size* of what should be possible to fabricate can be estimated, for the first time in many years it is not clear exactly *what* should be built, particularly in the area of nonvolatile memory (NVM), currently dominated by flash memory technology. Thus, the industry faces the prospect of a costly and risky switch from a known and established technology to something much less well known. Understandably, industry will often attempt to avoid such leaps, when possible.

466

The problem is not a possible failure to create a successful first product, because such failures are usually discovered at the advanced research or early development stage, when the level of investment is small and multiple alternative approaches are still being pursued. Instead, the disastrous scaling scenario is one in which the new technology works perfectly well for the first generation yet is doomed to failure immediately afterward. If only one or two device generations succeed, the NVM industry, having just invested heavily in this new technology, will be forced to make yet another switch and start the learning process all over again.

Thus, scaling studies are designed to consider the far future of the device road map, to try to uncover the roadblocks that may hinder a potential NVM technology at sizes much smaller than what can be built today. In the context of phase-change memory, we must consider the purpose the PCRAM cell will serve, along with possible failures, as the size of the cell scales down.

Critical device characteristics for a PCRAM cell include widely separated SET and RESET resistance distributions (necessary to create a margin of separation in order to avoid noise on fast readout), the ability to switch between these two states with electrical pulses that can be produced with the access device, the ability to read, or sense, the resistance states without perturbing them, high endurance (allowing many switching cycles between SET and RESET), long data retention (usually specified as a 10-year data lifetime at some elevated temperature), and fast SET speed (the time required to recrystallize the cell from the RESET state). Data retention usually depends on the ability of a cell to retain the amorphous RESET state by avoiding unintended recrystallization. An additional aspect that can be of significant importance is the ability to store more than one bit of data per cell, because this allows technologists to increase effective density without decreasing the feature

PCRAM cells have many possible points of failure. First, the underlying physics of the phase-change process could be completely different when the entire memory device essentially consists of interfaces only. Second, the threshold voltages for ultrascaled devices might be too close to the read voltages, thus creating a risk of accidental overwrites. If one looks sufficiently far into the future, the number of total atoms in a memory cell will become countable, which will likely require major rethinking with respect to doping with defect atoms, crystallization, melting and heat flow, and electrical tunneling effects.

In the next few technology generations, the most serious consideration is probably the need to ensure that the large currents required to switch PCRAM cells can be supplied by the associated access device. In a full memory array, an access device such as a diode or transistor must be included at each memory cell to ensure that the read and write currents on each bitline interact with only one memory device at a time. The amount of current that this access device can supply essentially sets the requirement for the phase-change memory element RESET current. One way to relax this requirement is to simply make the access device larger so that it can drive a larger current. However, because this choice sacrifices memory density and subsequently increases the cost per megabyte, this solution is not economically viable for a prospective memory technology.

A more tenable choice involves the use of the largest access device that does not sacrifice any density, along with a design of the phase-change memory cell such that the only current path through the device passes through a very small aperture. As this aperture shrinks in size, the volume of phase-change material that must be melted (and quenched into the amorphous state) to completely block the aperture is reduced. In turn, this decreases the power (and thus, the current) requirements. If this current is sufficiently low, then a minimum-size access device can provide sufficient power to switch the cell from its SET state to its RESET state. Although returning to the SET state involves exceeding the threshold voltage, the amount of power (and current) in the SET pulse is typically 40–80% of the RESET pulse. Thus, the RESET pulse usually must be considered when determining whether the access device will supply sufficient current, while the SET pulse is typically the factor that dictates the write speed of PCRAM technology.

Two general categories of cell structures exist for implementing a sublithographic aperture. One category involves the control of this cross-section by the size of one of the electrical contacts to the phase-change material [contact minimized, Figure 1(b)] [13–19]. The other category involves minimizing the size of the phase-change material itself at some point within the cell [volume minimized, or confined, Figure 1(c) [6, 13, 20-26]. When compared to contact-minimized cell structures, volumeminimized phase-change material structures have the advantage of offering a potentially lower RESET current for a given critical dimension [13, 21, 24], as well as the possibility for enhanced endurance. This possibility is supported by the observation that many failure and degradation mechanisms for PCRAM cells are associated with the interface between the phase-change material and one of the surrounding materials [27]. It is beneficial to keep the switching volume as contained as possible within the phase-change material and thus away from the electrodes.

On the other hand, in addition to some processing advantages mentioned in the section "Device integration issues of scaling," advantages exist for the contact-

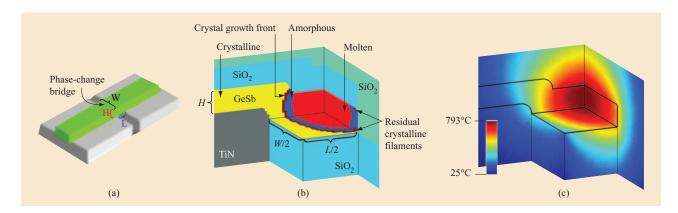

In the phase-change bridge (PCB) memory cell, (a) the cross-sectional area ( $W \times H$ ) has only one dimension that depends on lithographic patterning, making it possible to greatly reduce the second dimension via ultrathin films. (b) Simulated 3D distribution of material phase. (c) Temperature distribution within a PCB memory device during a RESET pulse, showing the receding melting spot as the device just begins to cool. A slightly higher pulse current would have melted the residual crystalline filaments at the device periphery, leading to a successful RESET. (Republished from Reference [6]; ©2006 IEEE.)

minimized design. For instance, because the switching volume occurs where a large expanse of phase-change material meets a narrow electrode, heat loss is reduced in both directions. In one direction, heat loss is low because of the inherently low thermal conductivity of the phase-change material. In the other direction, heat loss is low because the small cross-section of the electrode helps keep the overall thermal resistance high despite its high thermal conductivity.

Because of the large number of factors that can influence the RESET current, predictive numerical simulations are important. A number of studies have used analytical equations [28-31], finite-element techniques [21, 32–34], and finite-difference techniques [6, 35] to analyze either PCRAM cells or the phase-change material. Pirovano et al. [13] studied the RESET current and the thermal proximity effect of scaled PCRAM using both simulation and experiment. Although analytical techniques are attractively simple and work well for explaining the incubation of new crystalline nuclei [28] or threshold switching [29], it is difficult to include the effects of inhomogeneous temperature distributions and temperature-dependent resistivity, which critically affect the RESET current through their effect on the dynamic resistance of the cell. Finite-element techniques can include these effects but are difficult to extend to threedimensional cell designs. Finally, even though nucleation is unlikely to have an effect during the fast RESET pulse, recrystallization at the end of a RESET pulse does play an important role in the value of the RESET current, especially for the fastest-crystallizing phase-change materials that are potentially of the most use for

applications. The best-case scenario involves a simulation tool that provides results that could potentially be compared to fast electrical SET and RESET experiments, slow thin-film crystallization experiments, and optical-pulse experiments performed with the same material.

From our experience with such a simulation tool [6], the RESET condition is not dictated by the maximum temperature at the cell center, but by what happens at the edge of the cell. For instance, as shown in **Figure 2**, a voltage pulse just below the RESET condition invariably results in some small portion of the limiting cross-sectional aperture remaining in the crystalline state, usually at the extreme edges of the cell [6]. (The cell concept shown here, called the *phase-change bridge* [Figure 2(a)], is described in detail in the section "Scaling demonstrator: The phase-change bridge.")

In general, aside from the obvious choice of reducing the phase-change critical dimension, the best way to reduce the RESET current is to improve the efficiency with which injected electrical power heats the cell. Another popular way to decrease the RESET current is to increase the overall resistance of the cell by increasing the series resistance of the contact electrode [36].

Other considerations that need to be taken into account for scaling include possible decreases in supply voltage, concerns about whether devices will be able to retain data throughout the desired 10-year lifetime (at a maximum temperature that depends on the particular application), and sudden increases in failure mechanisms that could possibly arise at some future technology node (i.e., technology generation). While failure mechanisms are difficult to predict, Pirovano et al. [13] showed that at

468

least out to the 65-nm node, the thermal cross-talk between cells should remain sufficiently low that a 10-year lifetime will not be significantly reduced by writing data to neighboring cells.

### Phase-change materials

One of the most critical aspects of PCRAM technology involves the memory material itself. Most phase-change materials are chalcogenides, containing at least one element from group 6 of the periodic table, with GST being the most commonly used and most widely studied material. A notable exception is GeSb, which though not a chalcogenide is still a very promising phase-change material. Dozens of different phase-change materials have been developed [37–39], and the choice of available materials can be further widened by doping these materials [23, 40–42]. Examples of phase-change materials being investigated for PCRAM include the following: Ge-Te [43], GeSeTe<sub>2</sub> [44], AgSbSe<sub>2</sub> [45], Sb-Se [46], Ag-In-Sb-Te [47], and other Sb-Te variants [23, 48], along with a wide variety of dopants.

Researchers involved with phase-change technologies started to build devices using GST because it was one of the most commonly applied materials in optical storage; however, these materials had been originally selected by developers of optical storage because of the advantageous optical properties of the materials. Not surprisingly, these same materials have some disadvantages within PCRAM applications. For example, this large optical contrast (desirable for optical storage) is directly correlated with a large difference in mass density between the amorphous and crystalline phases [49], which can be as high as 7% or 8% for GST [50]. Such a large mass density change on switching could in fact be detrimental in a solid-state device, while optical contrast is of no consequence.

For successful development of PCRAM technology, the phase-change material needs to fulfill a number of properties simultaneously. Phase-change materials for PCRAM must have the appropriate crystallization speed. They should crystallize fast (e.g., in a few tens of nanoseconds) but not too fast; otherwise, melt-quenching becomes impossible. They should have relatively high resistivity in the crystalline phase in order to reduce the RESET current, yet the difference between the resistivities of the two phases should still be very large (greater than a factor of 100) in order to maintain a high on/off ratio. While a relatively low melting point is desirable for a reduction of the RESET current, a phase-change material needs to retain data at the operation temperature of the memory (~80–90°C for embedded memory and as high as 150°C for automotive applications). Thus, the crystallization temperature of a suitable material must be substantially higher than the operating temperature. High cyclability is of great importance for many applications,

so the material should not chemically react with its surroundings or deteriorate during repeated cycling. Finally, it should be possible to deposit the optimum material using CMOS-compatible deposition techniques such as sputter deposition or chemical vapor deposition.

# Scaling properties of phase-change materials

One aspect of scaling to consider for PCRAM technology is the behavior of the materials themselves when dimensions decrease. It is known that thin films or nanoparticles of a given material can have very different properties from their bulk counterparts. In order to predict the potential behavior of highly scaled PCRAM, it is important to find out how and at what film thickness or nanoparticle size the properties of phase-change materials might be influenced by size. Important properties that can be influenced by size are the crystallization temperature and the melting point, and this scaling behavior is likely to be a function of material as well.

Scaling of the materials has been studied by shrinking dimension (thin films) [51-54], two dimensions (nanowires) [55–59], and three dimensions (nanoparticles) [60-67] for a variety of phase-change materials. Thin films of GST and GeSb were studied with time-resolved x-ray diffraction (XRD). The films were deposited at room temperature and were amorphous as deposited. We found that the crystallization temperature increases as film thickness is reduced [51]. Films that are thinner than about 20 nm showed a higher temperature at which crystallization occurs than thick films and bulk material. For the thinnest films that still showed clear XRD peaks (1.3 nm thick for GeSb), crystallization occurs at about 300°C, while thick films crystallize at about 235°C. This increase in crystallization temperature indicates that data loss due to nucleation of new crystal nuclei within the amorphous portion of a scaled-down cell in the RESET state should actually be less likely than in a larger cell.

For thin GST films, the amorphous-fcc (face-centeredcubic) phase transition also shifts to higher temperatures for films thinner than 20 nm, and for films thinner than 3.6 nm, the fcc phase is no longer formed. Interestingly, the hexagonal phase is still formed in these very thin films of 3.6 nm and 2 nm, but no crystallization was observed in films thinner than 2 nm. As we discuss in the next section, it is indeed possible to fabricate functioning PCRAM cells with films as thin as 3 nm. Recording of information has also been demonstrated using 18-nm thin GST films [53], with recording densities up to 3.3 Tb/in<sup>2</sup> by applying a nanoheater atomic force microscopy (AFM) tip. With ultrathin GST films (1-5 nm), the smallest crystalline recording marks in an amorphous film that could be produced by an AFM tip were found to be about 10 nm in diameter [54], although these smallest

marks disappeared within minutes. On the other hand, slightly larger marks (20 nm) were stable for at least one hour. The reverse process was also demonstrated, and amorphous marks as small as about 10 nm were also recorded using AFM and scanning tunneling microscopy (STM) [52].

GST [55], GeTe [56–58], In<sub>2</sub>Se<sub>3</sub> [59], and Sb<sub>2</sub>Te [58] phase-change nanowires have been grown by the metal catalyst-mediated vapor-liquid-solid method. These nanowires were single crystals, with diameters ranging from 20 to 200 nm, depending on the size of the Au catalyst nanoparticles. In one case [58], GeTe nanowires with a helical structure were formed. Sun et al. [57] also found that the melting point of GeTe nanowires was significantly reduced to 390°C, which may be compared to the bulk melting point of GeTe of 725°C. Researchers have observed a reduction of the melting point for In<sub>2</sub>Se<sub>3</sub> nanowires [59], which melted at 680°C compared to a melting point of 890°C for bulk In<sub>2</sub>Se<sub>3</sub>. Switching devices were fabricated [55, 56] by contacting the GeTe nanowires employing a focused ion beam (FIB) technique to deposit Pt electrodes with a 2- $\mu$ m separation on a nanowire. In other words, two Pt contact pads are formed by the FIB, and these contacts can be used to make a connection with the larger metal tips of a tester in order to test the device. These devices showed clear thresholdswitching characteristics typical for phase-change devices and could repeatedly be switched between the amorphous and the crystalline phase using an electrical current pulse.

Phase-change nanoparticles have been fabricated and studied using a variety of methods. Pulsed-laser ablation was used to fabricate GST nanoparticles with sizes between 5 and 50 nm [57, 62, 63]. PCRAM devices have been fabricated using multiple layers of GST nanoparticles produced by laser ablation [57], and threshold switching as well as repeated switching of the devices has been demonstrated. Yoon et al. [63] reported that for particles exposed to 100°C, 200°C, 300°C, and 400°C, in all cases the particles had crystalline parts in the fcc phase, but they also observed other crystalline phases, presumably due to off-stoichiometric Ge-Sb-Te regions. Choi et al. [62] observed that crystallization of the nanoparticles occurred for temperatures between 200°C and 300°C, and that nanoparticles crystallized at these temperatures showed both the fcc and the hexagonal phase, while nanoparticles heated to temperatures higher than 400°C showed only the fcc phase. This is surprising because it has been shown that the fcc phase is the metastable phase in thick films and bulk GST, appearing at about 150°C and transformed into the stable hexagonal phase at about 350-400°C [68].

The crystallization behavior of large arrays of phasechange nanoparticles of various materials (GST, N-doped GST, GeSb, Sb<sub>2</sub>Te, and AIST) fabricated by electronbeam lithography have been studied using time-resolved XRD [67]. In this study, researchers observed that all nanoparticle arrays with particle sizes between 20 and 80 nm exhibited clear crystallization at temperatures similar to thick films of the same material with the exception of Sb<sub>2</sub>Te, which showed an increased crystallization temperature (40°C higher) compared to thick films. In particular, GST phase-change nanoparticles exhibited only the fcc phase for the smallest particles (20 nm), while larger particles exhibited a behavior similar to thick films and bulk material [67]. As mentioned earlier, GST thin films seem to behave differently from GST nanoparticles, with the thinnest films forming only the hexagonal phase but not the fcc phase.

To further reduce particle size, self-assembly-based lithographic techniques have been applied to fabricate phase-change nanoparticles [64–66]. Self-assembled PS-b-P4VP (polystyrene-b-polyvinylpyridine) on top of an amorphous GeSb phase-change film was used to locally grow SiO<sub>2</sub> dots on top of the P4VP domains [64, 65]. Reactive ion etching and ion milling were then applied to transfer the pattern into the GeSb using the SiO<sub>2</sub> dots as a hard mask, which can resist the subsequent etching and milling processes. Time-resolved XRD performed on the nanoparticle arrays demonstrated that these 15-nmdiameter particles clearly crystallize at a temperature that is 15°C lower than comparable thin film. Figure 3 shows the intensity of diffracted x-ray peaks acquired at an x-ray wavelength of 1.797 Å as a function of temperature during a 1°C/s heating of a GeSb phase-change nanoparticle array fabricated through self-assembly, and a cross-sectional bright-field transmission electron microscopic (TEM) image of the same GeSb nanoparticles. In another experiment, PS-b-PMMA [polystyrene-b-poly(methylmethacrylate)] films have been used, with phase-change nanoparticles fabricated by PMMA removal, deposition into the PS-b-PMMA template, and lift-off (i.e., removing the polymer) [66]. AIST nanoparticles of about 20 nm in diameter have been obtained that showed a crystallization temperature of 175°C, slightly higher than a blanket film (165°C).

A very different and nontraditional way of depositing phase-change materials involves the spin-on method. Novel spin-on phase-change materials have been developed [69, 70], and their excellent via-filling capabilities have been demonstrated [70]. By combining spin-on materials and self-assembly (GeSbSe spun-on phase-change material on a PS-b-PMMA template, with PMMA removal and subsequent lift-off), phase-change nanoparticles were produced that showed a crystallization temperature 35°C lower than for thick spin-on films.

470

Some of the smallest phase-change nanoparticles (sub-10-nm nanoparticles) that have been reported have been synthesized by solution-based chemistry [71]. These GeSe particles were crystalline after synthesis and monodisperse compared to particles fabricated by laser ablation. More studies are required to evaluate the properties of these particles and their potential to serve as memory material, but the fact that these small particles can be crystalline and show narrow size distributions makes them interesting candidates for future PCRAM applications.

# Scaling demonstrator: The phase-change bridge

There are several goals for studying the scaling behavior of a PCRAM device. Although simulations and analyses have long predicted that the RESET current should be reduced when the device dimensions are reduced [16], the exact value and rate of this reduction depends significantly on simulation parameters that are not always well known. Thus, the fabrication of devices that vary in size is critical for the quantitative calibration and verification of such models. In addition, experimental demonstration of prototype devices provides tangible proof that very small phase-change memory devices do indeed work. A number of aspects not easily apparent in simulation can be evaluated, such as changes either in the degradation mechanisms or in the phase-change dynamics in the presence of increased surface and interface effects.

Several groups have studied phase-change memory scaling [13, 23]. By measuring the RESET current experimentally, Pirovano et al. [13] showed that even when the contact area between the phase-change materials and the electrode is only about 300 nm<sup>2</sup>, devices still function properly. Lankhorst et al. [23] described a phase-change line device with cross-sectional areas as small as 225 nm<sup>2</sup> that could be switched repeatedly [23]. However, if we assume that the sublithographic size of the phase-change critical dimension will be equal to 30% of the smallest achievable lithographic dimension [12], then these 15-nm phase-change critical dimensions roughly correspond to a 45-nm lithography node, which will likely be in use by the flash memory industry as soon as 2009 [12]. In order to determine how PCRAM might operate further into the future, it is of great interest to try to further decrease device cross-section.

The device we have implemented in order to study scaling in actual devices, called the *phase-change bridge* (PCB) and shown in Figure 2(a), consists of a narrow line of ultrathin phase-change material bridging two underlying electrodes [6]. Unlike in earlier line-device concepts [23], the electrodes are formed very close together in order to obtain a reasonable threshold voltage and are separated by a small oxide gap that defines the

# Figure 3

GeSb nanoparticles. (a) Intensity of diffracted x-ray peaks as a function of temperature during a 1°C/s heating of GeSb phase-change nanoparticle arrays fabricated using self-assembly-based lithography. The data were acquired at an x-ray wavelength of 1.797 Å. (b) Cross-sectional bright-field TEM image of the same GeSb nanoparticles, demonstrating that sub-20-nm-sized particles crystallize at temperatures that are similar to bulk material.

bridge length L. The cross-sectional area ( $W \times H$ ) depends linearly on lithographic patterning, offering both reduced sensitivity to variations in the critical lithographic dimension and an alternative path for scaling to future technology nodes via ultrathin films.

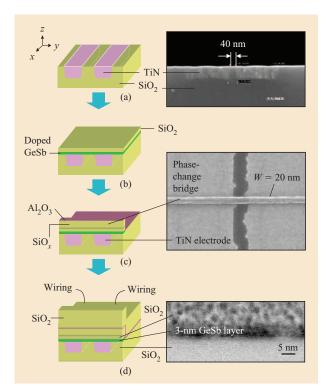

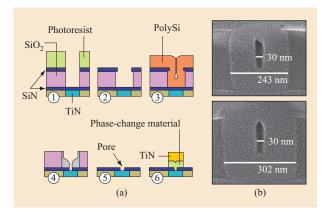

The process flow for the device in our study is shown in **Figure 4**, together with representative scanning electron microscope and TEM images. First, conventional 248-nm KrF lithography and etching was used to fabricate two parallel trenches in SiO<sub>2</sub> separated by a very narrow SiO<sub>2</sub> layer (from 40 nm to 500 nm). After filling in the trenches with thick Ti/TiN by sputter deposition and subsequent chemical-mechanical polishing, wafers were obtained with two TiN electrodes separated by a small SiO<sub>2</sub> gap [Figure 4(a)]. Doped GeSb phase-change material with thicknesses between 3 and 10 nm was then deposited using magnetron sputtering, followed immediately by a 10-nm SiO<sub>2</sub> cap layer to prevent oxidation of the phasechange material [Figure 4(b)]. Electron-beam lithography was then used to define the bridge structures with widths between 20 and 200 nm. After the final ion milling step, another cap layer of 5 nm of Al<sub>2</sub>O<sub>3</sub> was deposited onto the device without breaking vacuum to prevent oxidation

Schematic 3D plots are illustrated after each step for fabricating the bridge device. (a) 3D plot and cross-sectional SEM (scanning electron microscope) image after TiN electrode fabrication. (b) 3D plot after  $\mathrm{SiO}_2$  deposition. (c) 3D plot and a top-view SEM image after  $\mathrm{Al}_2\mathrm{O}_3$  encapsulation. (d) Schematic plot and cross-sectional TEM image after full fabrication. (Republished from Reference [6]; ©2006 IEEE.)

[Figure 4(c)]. To protect the whole device, a thick capping layer (50 nm of  $SiO_2$ ) was deposited before the device was wired for testing [Figure 4(d)].

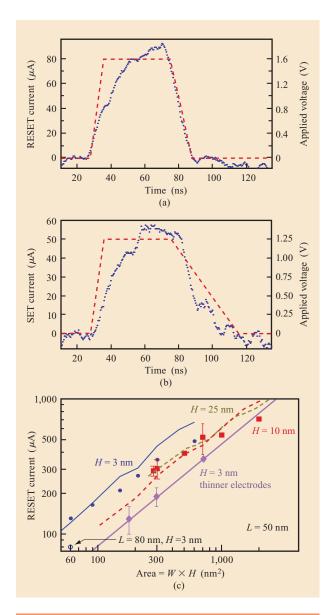

These PCB devices were electrically tested using a custom apparatus designed for prototype PCRAM devices. An arbitrary-waveform generator was used to produce current pulses with rise and fall times shorter than 2.5 ns. Such pulses are required because the doped GeSb material shows very fast recrystallization, as fast as 10-20 ns in optical characterization experiments [6]. The current-voltage characteristics of these devices exhibit both threshold switching and proper device performance (switching between SET and RESET states), even at the smallest cross-sectional areas of 60 nm<sup>2</sup> (H = 3 nm, W =20 nm). This rectangular cross-sectional area corresponds to a cylindrical phase-change critical dimension of 9 nm, commensurate with a minimum lithographic feature size of 30 nm. Thus, these PCB devices provide strong experimental evidence that PCRAM devices could

potentially scale at least through the 32-nm device generation, which the flash memory industry is expected to reach in the year 2013 [12].

SET pulses as short as 40 ns could be used to switch the PCB without sacrificing the ratio between the RESET and SET state resistances. Because such speeds are not easily obtained even in large GST-based devices, these results are due to the inherently fast switching found in doped GeSb phase-change materials. Optical testing of the raw material [6] also shows significant speed improvements compared to the GST material. Thus, this doped GeSb material offers a unique combination of fast switching, a very high difference in resistivity between the amorphous and crystalline phases (more than four orders of magnitude), high crystallization temperatures, and even the capability of operating using phase-change material thicknesses as small as 3 nm.

As predicted by simulations, the RESET current scales directly with the cross-sectional area of the device. A comparison of experimental results with simulation results for RESET current is shown in **Figure 5**. For the smallest devices fabricated in this study, with a cross-sectional area of 20 nm by 3 nm, the RESET current was as low as approximately 80  $\mu$ A. As predicted, the lowest RESET current was not obtained with the shortest device lengths [6]. This effect arises from a balance between the excessive heat loss to the metal electrodes that occurs at short lengths and the poor power efficiency that comes from distributed heating of a long PCB.

With careful design of the surrounding material and structure, the RESET current can potentially be further reduced. For instance, by modifying the process described above, we were able to fabricate PCB devices with 5-nmthick TaN electrodes (instead of 80-nm TiN). This allowed us to reduce the RESET current by roughly 40% (Figure 5).

Typically, PCB devices could be cycled through more than 10,000 SET-RESET cycles. Thermal retention was tested by measuring the resistance of a PCB device programmed into the RESET state while heating the device. As expected from the measured dependence of resistivity on temperature in doped GeSb, the device resistance decreases while heating. After heating to 175°C at a rate of 1°C/s, the device was cooled and the resistance was found to have returned to a high-resistivity state. A device fabricated from GST would have fully crystallized at these temperatures, losing the stored data. However, the final resistance in the doped GeSb device is approximately only 50% of the value of the initial resistance; thus, some small amount of recrystallization has taken place. Doped GeSb has an advantage because it moves the point at which data loss occurs to higher temperatures.

# **Device integration issues of scaling**

Prototype devices such as the PCB are ideal vehicles for fast testing of new materials because the fabrication turnaround time can be very short. This is especially true in comparison to the integration of arrays of PCRAM cells, each fabricated with its own access device in a full CMOS process. For such fully integrated wafers, a number of other concerns must be addressed. As mentioned earlier, the need to minimize the RESET current required by the phase-change memory cell and to maximize the current supplied by the access device are key issues for achieving a small size for the phase-change memory cell. In addition, while the read voltage, the RESET pulse, and the SET pulse can be optimized for the average memory cell, variations between cells and between access devices must be minimized so that these same choices can be used to successfully operate all the cells in the memory array.

Although alternative schemes exist [72], a diode or transistor is typically used as the access device. While a diode can provide a current-to-cell size advantage over a planar transistor at sizes as low as those used at the 16-nm node [73], the diode scheme is more vulnerable to errors induced by writing data to adjacent cells because of bipolar turn-on of the nearest-neighbor cells [25]. A 5.8- $F^2$  PCRAM diode cell has been demonstrated using a 90-nm technology in which the diode was able to supply 1.8 mA at 1.8 V [25]. (The term F refers to the smallest lithographic feature size of the respective lithographic technology node.) In comparison, a 90-nm 10- $F^2$  tri-gate FET could only supply approximately half of this current [25].

In order to fabricate a phase-change memory cell that will work even with these small currents, an innovative integration scheme is needed that creates a highly sublithographic, yet controllable, feature size. Subtle variations in cell design may have a significant impact on critical device characteristics, including endurance, retention, SET and RESET resistance distributions, and SET speed. The cell design must be scalable as well as highly manufacturable, because scaling implies not only a decrease in the physical dimension of the memory cell, but also an increase in the number of memory cells per chip. Finally, in order to maximize the number of bits per cell, a cell structure that allows multibit functionality is highly desirable [24, 74].

Many different types of cell structures have been proposed with the aim of not only minimizing the RESET current, but also improving reliability and performance and reducing the variability. Most notable are the mushroom cell [16], the pillar cell [24], the bridge cell [6], the microtrench cell [14], the pore cell [20, 22, 26], and the ring bottom electrode mushroom cell [15, 17–19].

# Figure 5

Typical measured current traces for (a) RESET and (b) SET steps of a prototype phase-change bridge memory cell with a 60-nm<sup>2</sup> cross-sectional area (H = 3 nm, W = 20 nm, L = 50 nm) and minimal encapsulation, corresponding to RESET (or SET) resistances of 500 k $\Omega$  (or 95 k $\Omega$  ). The red dashed line indicates applied voltage, as labeled on the right y-axis. The blue dotted line indicates the device current, as labeled on the left y-axis. (c) Measured (symbols) and simulated (lines) RESET current of prototype phase-change bridge memory cells as a function of bridge width W, for L = 50 nm and H = 3, 10, and 25 nm (simulation only). For comparison, the open symbol shows our lowest achieved RESET current (with 80-nm thick TiN electrodes) of roughly 80  $\mu$ A. The purple diamonds, along with a fit through the data to guide the eye, show the reduction in RESET current made possible when reducing the heat loss through the electrodes by reducing electrode thickness and changing from TiN to TaN. (Republished from Reference [6]; ©2006 IEEE.)

Sublithographic features. (a) A sublithographic-size lithographyindependent feature is fabricated using the keyhole-transfer process in a sequence of steps described in the text. (b) SEM cross-sectional image corresponding to step 3, showing keyholes for two different sized lithographically defined holes. Because the keyhole size does not depend on lithography, the phase-change critical dimension is decoupled from any lithographic variability.

When compared to contact-minimized cell structures, volume-minimized phase-change material structures have some potential advantages in terms of RESET current for a given critical dimension and in endurance (because the switching volume is kept away from material interfaces). However, the fabrication of such volume-minimized structures offers significant challenges, either in the filling in a sublithographic-sized feature with the phase-change material (microtrench and pore cells) or in the etching of a sublithographic line (bridge cell) or pillar (pillar cell) of phase-change material. Standard PVD (physical vapor deposition) sputter deposition techniques have been successful at filling low aspect-ratio pores [20, 26], and a deposition/etch/deposition process has been demonstrated for filling a 50-nm bottom criticaldimension 2:1 aspect-ratio pore [22]. A recent advancement in the confined phase-change memory cell was a demonstration of a high aspect-ratio pore cell filled with chemical vapor deposition (CVD) GST, polished after GST deposition, and capped with a top electrode material [75]. This fill-and-polish scheme has the additional advantage of avoiding possible damage of the phase-change material caused by the reactive ion etching process [25] that is normally required to isolate the device from its neighbors along adjacent bitlines.

The main advantage of the contact-minimized cell structures is the relative ease of fabrication associated with the phase-change material deposition and isolation processes. A sublithographic bottom electrode integration scheme (such as that used for a mushroom cell) forms a flat surface on which the phase-change material can be deposited with a standard PVD sputter deposition. In addition, the flat surface eliminates possible sources of stress associated with topography that could degrade reliability. Contact-minimized structures also naturally allow an optimization of the encapsulation material surrounding the phase-change material, since the encapsulating material can be deposited directly after the phase-change material isolation, independent of the previous processes. This encapsulation is important, as it has been found to help avoid oxygen penetration that can oxidize the interface between the bottom electrode and the phase-change material [18].

Various methods have been introduced to create sublithographic features. The creation of a pillar cell begins with a lithographically defined pillar of photoresist that is reduced in size through the use of a trimming reactive ion etching [24]. The mushroom cell and the microtrench cell make use of a lithographically defined hole [15] or trench [14], and the size is reduced using a spacer process. However, these methods tend to produce a sublithographic feature that inherits the criticaldimension variation associated with the lithographic dimension. Because the microtrench cell includes a bottom electrode whose line width is determined by deposition rather than lithography, only one of the two critical dimensions of the microtrench cell is dependent on lithography (as is the case for the PCB). The ring bottom electrode mushroom cell was introduced to reduce the dependence of the effective contact area of the bottom electrode on the variability of the size of the lithographyand spacer-defined contact hole [15], because the contact area of a thin annulus varies only linearly with its diameter. However, in all of these approaches, lithographic variations directly result in variations in diameter, which in turn cause the cell resistance to vary from device to device. Such variations have two effects. First, resistance variations reduce the distinction between the SET and RESET states, potentially leading to bit errors on readout. Second, variations in resistance will tend to change the temperature produced by a particular applied voltage, which increases the worst-case RESET pulse amplitude, reduces endurance by exposing some cells to much more RESET power than they really require, and unnecessarily complicates the design of a SET pulse that can successfully switch any cell in the memory array.

We have developed a keyhole-transfer process [26] that fully de-couples the variation associated with lithography from the sublithographic feature size. **Figure 6(a)** shows how the keyhole-transfer process creates a sublithographic critical dimension that is essentially independent of the original feature size by

combining accurate etch-back with conformal deposition into a lithographically defined hole. In step 1, a lithographically defined hole is etched into a SiN-SiO<sub>2</sub>-SiN stack stopping on the bottom SiN. Then, a selective wet etch (step 2) is used to recess the SiO<sub>2</sub> layer. In step 3, a highly conformal polySi film is deposited, producing a sublithographic keyhole in the polySi, whose diameter is equal to the recess of the SiO<sub>2</sub> layer. This keyhole is transferred (step 4) into the underlying SiN layer to define a pore. The SiO<sub>2</sub> layer and polySi are removed with a wet etch (step 5). The phase-change and top electrode (TiN) materials are deposited, and finally the cell is patterned (step 6) for isolation. Figure 6(b) demonstrates the ability to create a keyhole with a sublithographic feature size that is both less than 20% the size of the lithographically defined diameter and independent of variations in that larger hole diameter.

The keyhole-transfer process should scale well into future technology nodes. As the lithographically defined hole size becomes smaller, the amount of material through which the keyhole needs to be transferred [step 4 of Figure 6(a)] will simply become smaller because of the conformal nature of the film deposition [step 3 of Figure 6(a)]. Furthermore, this same keyhole-transfer process can also be used to construct a sublithographic-sized yet highly controlled bottom electrode for the mushroom cell.

Also under investigation is the utilization of a Ge nanowire as a bottom electrode for the mushroom cell [76]. This cell concept not only has the advantage that the bottom electrode size is controlled by the growth conditions of the nanowire, but also has the advantage that the n-type doped nanowire forms a diode at the connection to a p-type substrate and could potentially serve as the access device of the memory cell.

# Summary and outlook

In this paper, we have analyzed the scaling behavior of PCRAM technology in terms of the expected device properties, the scaling properties of the phase-change materials themselves, the performance of actual ultrascaled prototype devices, and the fabrication challenges that can be expected at future technology nodes. Simulations indicate that the critical value of the RESET current will continue to shrink rapidly with the size of the phase-change memory element. We show that the properties of phase-change materials are generally conserved with films that have thicknesses as small as only 10 nm, depending somewhat on the material. For thinner films, an increase in the crystallization temperature is observed that makes these films even better suited for PCRAM applications. Nanoparticles as small as 15 nm have been fabricated and still show crystallization at temperatures that are comparable to bulk material for

many cases. Functioning devices have been fabricated using films as thin as 3 nm, with cross-sectional areas of only 60 nm<sup>2</sup>. Integration schemes have been developed that can potentially implement such sublithographic critical dimensions within the phase-change memory cell, even in the presence of significant device-to-device variations in the lithographic patterning. Thus, in many aspects, PCRAM technology appears to be readily scalable to several future technology nodes.

# **Acknowledgments**

We want to acknowledge many people who contributed in some way to the work we have reviewed in this paper. The experimental device work described here (the phasechange bridge [23] and the keyhole-transfer process [26]) was performed as part of the IBM/Qimonda/Macronix PCRAM Joint Project, involving (in addition to the present authors) T. Nirschl, T. D. Happ, E. Joseph, A. Schrott, C. F. Chen, J. B. Philipp, R. Cheek, M.-H. Lee, W. P. Risk, G. M. McClelland, Y. Zhu, B. Yee, M. Lamorey, B. Rajendran, S. Zaidi, C. H. Ho, P. Flaitz, J. Bruley, R. Dasaka, S. Rossnagel, M. Yang, and R. Bergmann. We also gratefully acknowledge processing support from the Microelectronic Research Line at Yorktown Heights, New York, expert analytical and other support from the IBM Almaden Research Center (V. Deline, T. Topuria, A. Kellock, P. Rice, D. Miller, J.-J. Sweet, C. M. Jefferson, J. Cha, Y. Zhang, M. Caldwell, D. Mitzi, P. Green, and K. Appavoo), physical failure analysis (M. Hudson, L. Garrison, and M. Erickson), and valuable discussions with M. Wuttig, B. Kurdi, C. Narayan, K. Gopalakrishnan, R. Shenoy, W. Gallagher, R. Liu, G. Mueller, and T. C. Chen.

# References

- S. R. Ovshinsky, "Reversible Electrical Switching Phenomena in Disordered Structures," *Phys. Rev. Lett.* 21, No. 20, 1450–1455 (1968)

- N. Yamada, E. Ohno, K. Nishiuchi, and N. Akahira, "Rapid-Phase Transitions of GeTe-Sb<sub>2</sub>Te<sub>3</sub> Pseudobinary Amorphous Thin Films for an Optical Disk Memory," *J. Appl. Phys.* 69, No. 5, 2849–2856 (1991).

- 3. J. Tominaga, T. Kikukawa, M. Takahashi, and R. T. Phillips, "Structure of the Optical Phase Change Memory Alloy, Ag–V–In–Sb–Te, Determined by Optical Spectroscopy and Electron Diffraction," *J. Appl. Phys.* **82**, No. 7, 3214–3218 (1997).

- A. V. Kolobov, P. Fons, A. I. Frenkel, A. L. Ankudinov, J. Tominaga, and T. Uruga, "Understanding the Phase-Change Mechanism of Rewritable Optical Media," *Nature Mater.* 3, No. 3, 703–707 (2004).

- S. Hudgens and B. Johnson, "Overview of Phase-change Chalcogenide Nonvolatile Memory Technology," MRS Bull. 29, No. 11, 829–832 (2004).

- Y. C. Chen, C. T. Rettner, S. Raoux, G. W. Burr, S. H. Chen, R. M. Shelby, M. Salinga, et al., "Ultra-Thin Phase-Change Bridge Memory Device Using GeSb," *International Electron Devices Meeting*, San Francisco, CA, December 1–13, 2006, pp. 777–780.

- A. Pirovano, A. L. Lacaita, A. Benvenuti, F. Pellizzer, and R. Bez, "Electronic Switching in Phase-Change Memories," *IEEE Trans. Electr. Devices* 51, No. 3, 452–459 (2004).

- 8. D. Adler, H. K. Henisch, and N. Mott, "The Mechanism of Threshold Switching in Amorphous Alloys," *Rev. Mod. Phys.* **50**, No. 2, 209–220 (1978).

- A. Redaelli, A. Pirovano, F. Pellizzer, A. L. Lacaita,

D. Ielmini, and R. Bez, "Electronic Switching Effect and Phase-Change Transition in Chalcogenide Materials," *IEEE Electron Device Lett.* 25, No. 10, 684–686 (2004).

- D. Ielmini, A. L. Lacaita, and D. Mantegazza, "Recovery and Drift Dynamics of Resistance and Threshold Voltages in Phase-Change Memories," *IEEE Trans. Electron Devices* 54, No. 2, 308–315 (2007).

- A. Pirovano, A. L. Lacaita, F. Pellizzer, S. A. Kostylev, A. Benvenuti, and R. Bez, "Low-Field Amorphous State Resistance and Threshold Voltage Drift in Chalcogenide Materials," *IEEE Trans. Electron Devices* 51, No. 5, 714–719 (2004).

- International Technical Roadmap for Semiconductors, 2006; see http://www.itrs.net/Links/2006Update/2006UpdateFinal. htm

- A. Pirovano, A. L. Lacaita, A. Benvenuti, F. Pellizzer, S. Hudgens, and R. Bez, "Scaling Analysis of Phase-Change Memory Technology," *IEEE International Electron Devices Meeting*, December 8–10, 2003, pp. 29.6.1–29.6.4.

- F. Pellizzer, A. Pirovano, F. Ottogalli, M. Magistretti, M. Scaravaggi, P. Zuliani, M. Tosi, et al., "Novel muTrench Phase-Change Memory Cell for Embedded and Stand-alone Non-volatile Memory Applications," *Symposium on VLSI Technology*, 2004, pp. 18–19.

- S. J. Ahn, Y. N. Hwang, Y. J. Song, S. H. Lee, S. Y. Lee, J. H. Park, C. W. Jeong, et al., "Highly Reliable 50nm Contact Cell Technology for 256Mb PRAM," Symposium on VLSI Technology, Digest of Technical Papers, 2005, pp. 98–99.

- S. Lai and T. Lowrey, "OUM—A 180 nm Nonvolatile Memory Cell Element Technology for Stand Alone and Embedded Applications," *International Electron Devices Meeting, Technical Digest*, Washington, DC, December 2–5, 2001, pp. 3651–3654.

- C. W. Jeong, S. J. Ahn, Y. N. Hwang, Y. J. Song, J.-H. Oh, S.-Y. Lee, S.-H. Lee, et al., "Highly Reliable Ring-Type Contact for High-Density Phase Change Memory," *Jpn. J. Appl. Phys.* 45, No. 4B, 3233–3237 (2006).

- 18. Y. Song, K. Ryoo, Y. Hwang, C. Jeong, D. Lim, S. Park, J. Kim, et al., "Highly Reliable 256Mb PRAM with Advanced Ring Contact Technology and Novel Encapsulating Technology," Symposium on VLSI Technology, Digest of Technical Papers, 2006, pp. 15–16.

- K.-C. Ryoo, Y. J. Song, J.-M. Shin, S.-S. Park, D.-W. Lim, J.-H. Kim, W.-I. Park, et al., "Ring Contact Electrode Process for High Density Phase Change Random Access Memory," *Jpn. J. Appl. Phys.* 46, No. 4B, 2001–2005 (2007).

- S. Tyson, G. Wicker, T. Lowrey, S. Hudgens, and K. Hunt, "Nonvolatile, High Density, High Performance Phase-Change Memory," *IEEE Aerospace Conference Proceedings*, Vol. 5, Big Sky, MT, March 18–25, 2000, pp. 385–390.

- Y.-T. Kim, Y.-N. Hwang, K.-H. Lee, S.-H. Lee, C.-W. Jeong, S.-J. Ahn, F. Yeung, et al., "Programming Characteristics of Phase Change Random Access Memory Using Phase Change Simulations," *Jpn. J. Appl. Phys.* 44, No. 4B, 2701–2705 (2005).

- S. L. Cho, J. H. Yi, Y. H. Ha, B. J. Kuh, C. M. Lee, J. H. Park, S. D. Nam, et al., "Highly Scalable On-Axis Confined Cell Structure for High Density PRAM Beyond 256Mb," Symposium on VLSI Technology, Digest of Technical Papers, 2005, pp. 96–97.

- M. H. Lankhorst, B. W. Ketelaars, and R. A. Wolters, "Low-Cost and Nanoscale Non-volatile Memory Concept for Future Silicon Chips," *Nat. Mater.* 4, No. 4, 266–266 (2005).

- T. Happ, M. Breitwisch, A. Schrott, J. B. Philipp, M. Lee,

R. Cheek, T. Nirschl, et al., "Novel One-Mask Self-Heating

- Pillar Phase Change Memory," Symposium on VLSI Technology, Digest of Technical Papers, 2006, pp. 120–121.

- J. H. Oh, J. H. Park, Y. S. Lim, H. S. Lim, Y. T. Oh, J. S. Kim, J. M. Shin, et al., "Full Integration of Highly Manufacturable 512Mb PRAM Based on 90nm Technology," *International Electron Devices Meeting*, San Francisco, CA, 2006, pp. 49–52.

- M. Breitwisch, T. Nirschl, C. F. Chen, Y. Zhu, M. H. Lee, M. Lamorey, G. W. Burr, et al., "Novel Lithography-Independent Pore Phase Change Memory," *Symposium on VLSI Technology, Digest of Technical Papers*, 2007, pp. 100–101.

- A. Pirovano, A. Redaelli, F. Pellizzer, F. Ottogalli, M. Tosi,

D. Ielmini, A. L. Lacaita, and R. Bez, "Reliability Study of Phase-Change Nonvolatile Memories," *IEEE Trans. Device Mater. Rel.* 4, No. 3, 422–427 (2004).

- S. Senkader and C. D. Wright, "Models for Phase-Change of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> in Optical and Electrical Memory Devices," J. Appl. Phys. 95, No. 2, 504–511 (2004).

- D. Ielmini and Y. Zhang, "Physics-Based Analytical Model of Chalcogenide-Based Memories for Array Simulation," *International Electron Devices Meeting, Technical Digest*, Washington, DC, 2006, pp. 401–404.

- S.-B. Kim and H.-S. P. Wong, "Generalized Phase Change Memory Scaling Rule Analysis," Non-Volatile Semiconductor Memory Workshop, Monterey, CA, 2006, pp. 92–94.

- C. D. Wright, K. Blyuss, and P. Ashwin, "Master-Equation Approach to Understanding Multistate Phase-Change Memories and Processors," *Appl. Phys. Lett.* 90, No. 6, 63113 (2007).

- 32. G. Wicker, S. Tyson, T. Lowrey, S. Hudgens, R. Pugh, and K. Hunt, "Nonvolatile, High Density, High Performance Phase Change Memory," *Proceedings of SPIE*, Vol. 3891, 1999, pp. 2–9.

- T. Gille, L. Goux, J. Lisoni, K. De Meyer, and D. J. Wouters, "Impact of Material Crystallization Characteristics on the Switching Behavior of the Phase Change Memory Cell," MRS Symposium Proceedings, Vol. 918, Chalcogenide Alloys for Reconfigurable Electronics, 2006; ISBN 978-1-55899-875-9.

- Y. Yin, H. Sone, and S. Hosaka, "Finite Element Analysis of Dependence of Programming Characteristics of Phase-Change Memory on Material Properties of Chalcogenides," *Jpn. J. Appl. Phys.* 45, No. 11, 8600–8603 (2006).

- D. H. Kim, F. Merget, M. Forst, and H. Kurz, "Three-Dimensional Simulation Model of Switching Dynamics in Phase Change Random Access Memory Cells," *J. Appl. Phys.* 101, No. 6, 64512–64524 (2007).

- 36. W. Czubatyj, T. Lowrey, S. Kostylev, and I. Asano, "Current Reduction in Ovonic Memory Devices," *Proceedings of the European Phase Change and Ovonic Science Symposium*, Grenoble, France, 2006, pp. 143–152; see <a href="http://www.epcos.org/library/papers/pdf\_2006/pdf\_Invited/Czubatyj.pdf">http://www.epcos.org/library/papers/pdf\_2006/pdf\_Invited/Czubatyj.pdf</a>.

- L. van Pieterson, M. H. R. Lankhorst, M. van Schijndel,

A. E. T. Kuiper, and J. H. J. Roosen, "Phase-Change Recording Materials with a Growth-Dominated Crystallization Mechanism: A Materials Overview," *J. Appl. Phys.* 97, No. 8, 83520–83527 (2005).

- L. van Pieterson, M. van Schijndel, and J. C. N. Rijpers, "Te-Free, Sb-Based Phase-Change Materials for High-Speed Rewritable Optical Recording," *Appl. Phys. Lett.* 83, No. 7, 1373–1375 (2003).

- E. G. Yeo, L. P. Shi, R. Zhao, and T. C. Chong, "Investigation on Ultra-high Density and High Speed Nonvolatile Phase Change Random Access Memory (PCRAM) by Material Engineering," MRS Symposium Proceedings, Vol. 918, Chalcogenide Alloys for Reconfigurable Electronics, 2006; ISBN 978-1-55899-875-9.

- S. J. Ahn, Y. J. Song, C. W. Jeong, J. M. Shin, Y. Fai, Y. N. Hwang, S. H. Lee, et al., "Highly Manufacturable High Density Phase Change Memory of 64Mb and Beyond,"

- International Electron Devices Meeting, IEDM Technical Digest, San Francisco, CA, 2004, pp. 907–910.

- S. W. Ryu, J. H. Oh, B. J. Choi, S.-Y. Hwang, S. K. Hong, C. S. Hwang, and H. J. Kim, "SiO<sub>2</sub> Incorporation Effect in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Films Prepared by Magnetron Sputtering for Phase Change Random Access Memory Devices," *Electrochem.* Solid-State Lett. 9, No. 8, G259–G261 (2006).

- S. Raoux, M. Salinga, J. Jordan-Sweet, and A. Kellock, "Effect of Al and Cu Doping on the Crystallization Properties of the Phase Change Materials SbTe and GeSb," *J. Appl. Phys.* 101, No. 4, 44909–44915 (2007).

- M. Chen, K. A. Rubin, and R. W. Barton, "Compound Materials for Reversible, Phase-Change Optical Data Storage," *Appl. Phys. Lett.* 49, No. 9, 502–504 (1986).

- 44. H. B. Chung, K. Shin, and J. M. Lee, "Phase-Change Characteristics of Chalcogenide Ge<sub>1</sub>Se<sub>1</sub>Te<sub>2</sub> Thin Films for Use in Nonvolatile Memories," *J. Vac. Sci. Technol.* A25, No. 1, 48–53 (2007).

- K. Wang, C. Steimer, R. Detemple, D. Wamwangi, and M. Wuttig, "Assessment of Se Based Phase Change Alloy as a Candidate for Non-volatile Electronic Memory Applications," *Appl. Phys. A* 81, No. 8, 1601–1605 (2005).

- S. M. Yoon, N. Y. Lee, S. O. Ryu, K. J. Choi, Y. S. Park, S. Y. Lee, B. G. Yu, M. J. Kang, S. Y. Choi, and M. Wuttig, "Sb-Se-Based Phase-Change Memory Device with Lower Power and Higher Speed Operations." *IEEE Electron Device Lett.* 27, No. 6, 445–447 (2006).

- H. Iwasaki, M. Harigaya, O. Nonoyama, Y. Kageyama, M. Takahashi, K. Yamada, H. Deguchi, and Y. Ide, "Completely Erasable Phase Change Optical Disc II: Application of Ag-In-Sb-Te Mixed-Phase System for Rewritable Compact Disc Compatible with CD-Velocity and Double CD-Velocity," *Jpn. J. Appl. Phys.* 32, No. 11B, 5241–5247 (1993).

- B. Liu, Z. T. Song, S. L. Feng, and B. M. Chen,

"Characteristics of Chalcogenide Nonvolatile Memory Nano-Cell-Element Based on Sb<sub>2</sub>Te<sub>3</sub> Material," *Microelectr. Engin.* 82, No. 2, 168–174 (2005).

- R. Detemple, D. Wamwangi, M. Wuttig, and G. Bihlmayer, "Identification of Te Alloys with Suitable Phase Change Characteristics," *Appl. Phys. Lett.* 83, No. 13, 2572–2574 (2003).

- R. Detemple, I. Friedrich, W. Njoroge, I. Thomas, V. Weidenhof, H.-G. Wöltgens, S. Ziegler, and M. Wuttig, "Microscopic Studies of Fast Phase Transformations in GeSbTe Films," Materials Research Society Proceedings, Vol. 674, 2001; see http://stinet.dtic.mil/cgi-bin/GetTRDoc? AD=ADP012319&Location=U2&doc=GetTRDoc.pdf.

- S. Raoux, C. T. Rettner, J. Jordan-Sweet, V. R. Deline, J. B. Philipp, and H.-L. Lung, "Scaling Properties of Phase Change Nanostructures and Thin Films," *Proceedings of the European Symposium on Phase Change and Ovonic Science*, Grenoble, France, May 2006, pp. 127–134.

- H. Satoh, K. Sugawara, and K. Tanaka, "Nanoscale Phase Changes in Crystalline Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Films Using Scanning Probe Microscopes," *J. Appl. Phys.* 99, No. 2, 024306 (2006).

- 53. H. F. Hamann, M. O'Boyle, Y. C. Martin, M. Rooks, and H. K. Wickramasinghe, "Ultra-High-Density Phase-Change Storage and Memory," *Nat. Mater.* 5, No. 5, 383–387 (2006).

- T. Gotoh, K. Sugawara, and K. Tanaka, "Minimal Phase-Change Marks Produced in Amorphous Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Films," Jpn. J. Appl. Phys. 43, No. 6B, L818–L821 (2004).

- Y. Jung, S.-H. Lee, D.-K. Ko, and R. Agarwal, "Synthesis and Characterization of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Nanowires with Memory Switching Effect," *J. Am. Chem. Soc.* 128, No. 43, 14026–14027 (2006).

- S.-H. Lee, D.-K. Ko, Y. Jung, and R. Agarwal, "Size-Dependent Phase Transition Memory Switching Behavior and Low Writing Currents in GeTe Nanowires," *Appl. Phys. Lett.* 89, No. 22, 223116 (2006).

- X. Sun, B. Yu, and M. Meyyappan, "Synthesis and Nanoscale Thermal Encoding of Phase-Change Nanowires," *Appl. Phys. Lett.* 90, No. 18, 183116 (2007).

- S. Meister, H. Peng, K. McIlwrath, K. Jarausch, X. F. Zhang, and Y. Cui, "Synthesis and Characterization of Phase-Change Nanowires," *Nano Lett.* 6, No. 7, 1514–1517 (2006).

- X. Sun, B. Yu, G. Ng, T. D. Nguyen, and M. Meyyappan, "III-VI Compound Semiconductor Indium Selenide (In<sub>2</sub>Se<sub>3</sub>) Nanowires: Synthesis and Characterization," *Appl. Phys. Lett.* 89, No. 23, 233121 (2006).

- D. S. Suh, E. Lee, K. H. P. Kim, J. S. Noh, W. C. Shin, Y. S. Kang, C. Kim, Y. Khang, H. R. Yoon, and W. Jo, "Nonvolatile Switching Characteristics of Laser-ablated Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Nanoparticles for Phase-Change Memory Applications," *Appl. Phys. Lett.* 90, No. 2, 023101 (2007).

- B. F. Soares, F. Jonson, and N. I. Zheludev, "All-Optical Phase-Change Memory in a Single Gallium Nanoparticle," *Phys. Rev. Lett.* 98, No. 15, 153905 (2007).

- H. S. Choi, K. S. Seol, K. Takeuchi, J. Fujita, and Y. Ohki, "Synthesis of Size- and Structure-Controlled Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Nanoparticles," *Jpn. J. Appl. Phys.* 44, No. 10, 7720–7722 (2005)

- H. R. Yoon, W. Jo, E. H. Lee, J. H. Lee, M. Kim, K. Y. Lee, and Y. Khang, "Generation of Phase-Change Ge-Sb-Te Nanoparticles by Pulsed Laser Ablation," *J. Non-Cryst. Solids* 351, No. 43, 3430–3434 (2005).

- 64. Y. Zhang, H.-S. P. Wong, S. Raoux, J. N. Cha, C. T. Rettner, L. E. Krupp, T. Topuria, D. J. Milliron, P. M. Rice, and J. Jordan-Sweet, "Phase Change Nanodot Arrays Fabricated Using a Self-Assembly Diblock Copolymer Approach," *Appl. Phys. Lett.* 91, No. 13, 13104 (2007).

- J. N. Cha, Y. Zhang, H.-S. P. Wong, S. Raoux, C. Rettner, L. Krupp, and V. Deline, "Biomimetic Approaches for Fabricating High-Density Nanopatterned Arrays," *Chem. Mater.* 19, No. 4, 839–843 (2007).

- 66. S. Raoux, Y. Zhang, D. Milliron, J. Cha, M. Caldwell, C. T. Rettner, J. Jordan-Sweet, and H.-S. P. Wong, "X-ray Diffraction Studies of Phase Change Nanoparticles Produced by Self-Assembly-Based Lithographic Techniques," Proceedings of the European Symposium on Phase Change and Ovonic Science, Zermatt, Switzerland, September 2007, paper F01-19

- 67. S. Raoux, C. T. Rettner, J. L. Jordan-Sweet, A. J. Kellock, T. Topuria, P. M. Rice, and D. C. Miller, "Direct Observation of Amorphous to Crystalline Phase Transitions in Nanoparticle Arrays of Phase Change Materials," *J. Appl. Phys.* 102, No. 9, 94305 (2007).

- 68. I. Friedrich, V. Weidenhof, W. Njoroge, P. Franz, and M. Wuttig, "Structural Transformations of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Films Studied by Electrical Resistance Measurements," *J. Appl. Phys.* 87, No. 9, 4130–4134 (2000).

- D. B. Mitzi, S. Raoux, A. G. Schrott, M. Copel, A. Kellock, and J. Jordan-Sweet, "Solution-Based Processing of the Phase-Change Material KSb<sub>5</sub>S<sub>8</sub>," *Chem. Mat.* 18, No. 26, 6278–6282 (2006).

- D. Milliron, S. Raoux, R. S. Shelby, and J. Jordan-Sweet, "Solution-Phase Deposition and Nanopatterning of GeSbSe Phase-Change Materials," *Nat. Mat.* 6, No. 5, 352–356 (2007).

- M. Caldwell, S. Raoux, D. J. Milliron, and H.-S. P. Wong, "Synthesis and Characterization of Germanium Chalcogenide Nanoparticles via Single-Source Precursors and Coprecipitation," American Chemical Society 234th National Meeting and Exposition, Boston, MA, August 19–23, 2007; see http://oasys2.confex.com/acs/234nm/techprogram/ P1103272.HTM.

- Y.-C. Chen, C. F. Chen, C. T. Chen, J. Y. Yu, S. Wu, S. L. Lung, R. Liu, and C.-Y. Lu, "An Access-Transistor-Free (0T/1R) Non-volatile Resistance Random Access Memory (RRAM) Using a Novel Threshold Switching, Self-Rectifying Chalcogenide Device," *IEEE International Electron Devices Meeting, IEDM Technical Digest*, 2003, pp. 37.4.1–37.4.4.

- H.-L. Lung, M. Breitwisch, T. Happ, and C. Lam, "Phase-Change Memory—Present and Future," *Proceedings of the Second International Conference on Memory Technology and Design*, Giens, France, May 7–10, 2007, pp. 35–38; see <a href="http://">http://</a>

- www.icmtd.com/Proceeding/PROCEEDINGS%20-%20ICMTD2007.pdf.

- T. Nirschl, J. B. Philipp, T. D. Happ, G. W. Burr,

B. Rajendran, M.-H. Lee, A. Schrott, et al., "Write Strategies for 2 and 4-Bit Multi-level Phase-Change Memory," *IEEE International Electron Devices Meeting*, Washington, DC, 2007, pp. 461–464.

- J. I. Lee, H. Park, S. L. Cho, Y. L. Park, B. J. Bae, J. H. Park, J. S. Park, et al., "Highly Scalable Phase Change Memory with CVD GeSbTe for Sub 50nm Generation," *IEEE Symposium* on VLSI Technology, Kyoto, Japan, 2007, pp. 102–103.

- Y. Zhang, S. B. Kim, J. P. McVittie, H. Jagannathan, J. B. Ratchford, C. E. D. Chidsey, Y. Nishi, and H.-S. P. Wong, "An Integrated Phase Change Memory Cell with Ge Nanowire Diode For Cross-Point Memory," *IEEE Symposium on VLSI Technology*, Tokyo, Japan, 2007, pp. 98–99, 2007.

Received September 20, 2007; accepted for publication October 12, 2007; Internet publication July 10, 2008

Simone Raoux IBM/Oimonda/Macronix PCRAM Joint Project, IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (simone raoux@almaden.ibm.com). Dr. Raoux is a Research Staff Member at the IBM Almaden Research Center. She received her M.S. degree in 1984 and her Ph.D. degree in physics in 1988 both from Humboldt University, Berlin, Germany. From 1988 to 1991, she worked as a Staff Scientist at the Institute for Electron Physics in Berlin, Germany, performing research in the field of electrical breakdown. From 1992 to 2000, she was a Staff Scientist at Lawrence Berkeley National Laboratory and performed research in the fields of vacuum arc deposition, ion implantation, photoemission electron microscopy, x-ray magnetic circular dichroism, and near-edge x-ray absorption fine structure spectroscopy. Her current research interests include the physics and materials science of phase-change materials. Dr. Raoux is author or coauthor of more than 100 journal articles and holds 8 patents.

Geoffrey W. Burr IBM/Qimonda/Macronix PCRAM Joint Project, IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (burr@almaden.ibm.com). Dr. Burr received his B.S. degree in electrical engineering from the State University of New York at Buffalo in 1991 and his M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology in 1993 and 1996, respectively. Since that time, Dr. Burr has worked at the IBM Almaden Research Center, where he is currently a Research Staff Member. After having worked for a number of years as an experimentalist in volume holographic data storage and optical information processing, his current research interests include nanophotonics, numerical modeling for design optimization, phase-change memory, and other nonvolatile memory.

Matthew J. Breitwisch IBM/Qimonda/Macronix PCRAM Joint Project, IBM Thomas J. Watson Research Center, Yorktown Heights, New York 10598 (breitm@us.ibm.com).

Dr. Breitwisch is a Senior Engineer at the IBM T. J. Watson Research Center. He received a B.S. degree in physics, mathematics, and astrophysics from the University of Wisconsin at Madison in 1994 and a Ph.D. degree in physics from Iowa State University in 1999. He subsequently joined IBM at the IBM Microelectronics Center in Essex Junction, Vermont, where he has worked on developing low-standby-power SRAM, and on dc and RF compact models for CMOS FETs and passive devices. In 2005, Dr. Breitwisch joined the exploratory memory group at the T. J. Watson Research Center and has since worked on integration schemes for phase-change memory devices. He is an author or coauthor of 9 patents and 22 technical papers.

Charles T. Rettner IBM/Qimonda/Macronix PCRAM Joint Project, IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (rettner@almaden.ibm.com). Dr. Rettner is Research Staff Member at the IBM Almaden Research Center. He received his Ph.D. degree in chemistry from the University of Birmingham in 1978. After postdoctoral work at MIT and Stanford, he joined IBM in 1983. Until the early 1990s, his work mostly concerned the dynamics of chemical reactions, especially at surfaces. After working on a variety of problems relevant to magnetic recording, he has become increasingly involved with nanofabrication and electron-beam lithography. His current research interests include phase-change memory and nanomagnetic devices. He is author or coauthor of more than 170 journal articles and holds 15 patents.

Yi-Chou Chen IBM/Qimonda/Macronix PCRAM Joint Project, Advanced Memory Research Department (ME130), Emerging Central Lab/Macronix International Company Ltd, No. 16 Li-Hsin Road, Science Park, Hsinchu, Taiwan (melchen@mxic.com.tw). Dr. Chen is a Deputy Department Manager at Macronix. He received a B.S. degree and a Ph.D. degree in chemical engineering in 1995 and 2000, respectively, both from National Taiwan University. In 2000, he joined Macronix and worked on technology development of lithography, moving to the Emerging Central Lab in 2001, where he started working on phase-change memory. From 2005 to 2007, he was on assignment at the IBM Almaden Research Center. His current research interests include both phase-change materials and memory devices.

Robert M. Shelby IBM/Qimonda/Macronix PCRAM Joint Project, IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (shelby@almaden.ibm.com). Dr. Shelby received his B.S. degree from the California Institute of Technology in 1972 and his Ph.D. degree from the University of California in 1978, both in chemistry. He has been a Research Staff Member at IBM Almaden Research Center since 1979. His research has included nonlinear laser spectroscopy of defects in solids, frequency-domain data storage, the generation of squeezed light, optical quantum nondemolition measurement, squeezed optical solitons, and holographic data storage. Recently, he has worked on the characterization and study of phase-change materials for nonvolatile solid-state memory. He is a Fellow of the Optical Society of America.

Martin Salinga 1. Physikalisches Institut 1A, RWTH Aachen, Aachen, Germany (martin.salinga@physik.rwth-aachen.de).

Dr. Salinga is a staff member at the University of Technology (RWTH) Aachen, Germany. He obtained his diploma in 2004 and his Ph.D. degree in 2008, both in physics, from RWTH Aachen. For his diploma thesis on the kinetics of crystal nucleation and growth of phase-change materials used in optical data storage, he performed his research both at RWTH Aachen and at the Division of Engineering and Applied Sciences at Harvard University. From February 2005 until September 2006, he was on assignment at the IBM Almaden Research Center, investigating both crystallization kinetics and electronic properties of phase-change materials. Back at RWTH Aachen, Dr. Salinga continues his studies on phase-change materials while also teaching.

Daniel Krebs 1. Physikalisches Institut 1A, RWTH Aachen, Aachen, Germany (krebs@physik.rwth-aachen.de); IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (dkrebs@us.ibm.com). Mr. Krebs is a Ph.D. student at the 1. Physikalisches Institut 1A of RWTH Aachen University. In 2006, he received his diploma degree in physics at the RWTH Aachen University. From July 2007 to March 2008, he was on assignment at the IBM Almaden Research Center. Back at RWTH, he is currently working toward the understanding of the mechanism of threshold switching in phase-change materials.

Shih-Hung Chen IBM/Qimonda/Macronix PCRAM Joint Project, Macronix International Company Ltd., IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598; No. 16 Li-Hsin Road, Science Park, Hsinchu, Taiwan (shihhongchen@mxic.com.tw). Mr. Chen is a Senior Researcher at Macronix International Company. He obtained his M.S. degree in electrophysics in 1995 from National Chiao-Tung University and joined Macronix in 1997. Before performing research on phase-change memory, he managed a group working

on flash memory integration. In the field of phase-change memory, he has worked mainly on integration and physical failure analysis. He is currently working on product engineering and electrical failure analysis.

Hsiang-Lan Lung IBM/Qimonda/Macronix PCRAM Joint Project, Macronix International Company Ltd., IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (lunghl@us.ibm.com). Dr. Lung received his B.S. degree in material science and engineering from Feng Chia University in Taiwan in 1991, and his M.S. degree in material science and engineering from National Cheng Kung University in Taiwan in 1996. Since this time, Dr. Lung has worked at Macronix in Hsinchu, Taiwan. He received his Ph.D. degree in material science and engineering from National Tsing Hua University, Taiwan, in 2003. Currently, he is manager of the phase-change memory project at Macronix. Before this, Dr. Lung joined or managed several nonvolatile memory projects at Macronix, including projects involving MROM, NOR flash, NROM, FeRAM, and PCRAM. He is author or coauthor of 25 technical papers and holds 35 patents.

Chung H. Lam IBM/Qimonda/Macronix PCRAM Joint Project, IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (clam@us.ibm.com). Dr. Lam received his B.Sc. degree in electrical engineering at Polytechnic University of New York in 1978, and joined IBM General Technology Division in Burlington in 1978 as a memory circuit designer. In 1984, he was awarded the IBM Resident Study Fellowship and received his M.Sc. and Ph.D. degrees, both in electrical engineering, at Rensselaer Polytechnic Institute in 1987 and 1988, respectively. Upon returning from Resident Study at Rensselaer Polytechnic Institute, Dr. Lam assumed responsibilities in various disciplines of semiconductor research and development, including circuit and device design as well as process integration for memory and logic applications in IBM Microelectronics Division. He has a strong interest in nonvolatile memory devices and has been a member of the Technical Committee of the IEEE Non-Volatile Memory Workshop since 2001. In 2003, Dr. Lam transferred to IBM Research Division and was named Distinguished Engineer in 2007. He has managed the phase-change memory research project at the IBM Research Division in the T. J. Watson Research Center since 2003.