Towards a disruptively low-cost solid-state non-volatile memory

Science & Technology

#### January 2013

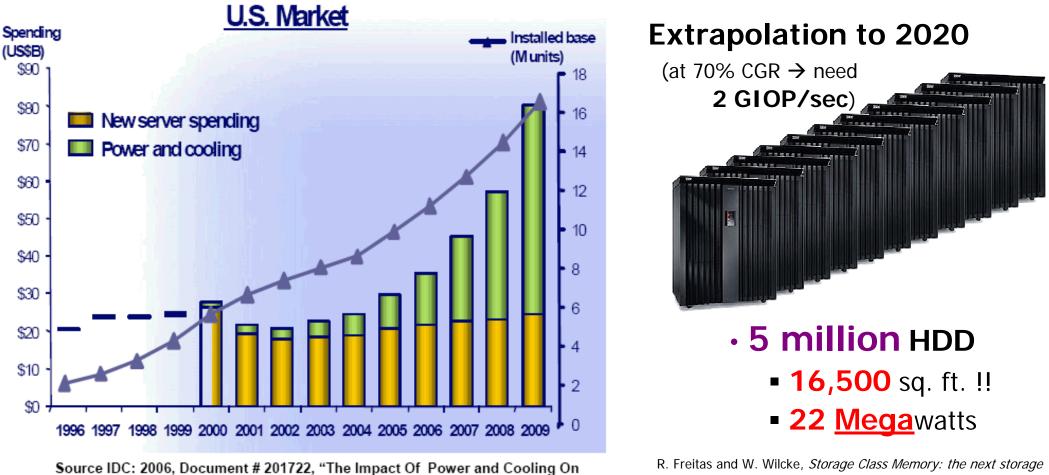

## Power & space in the server room

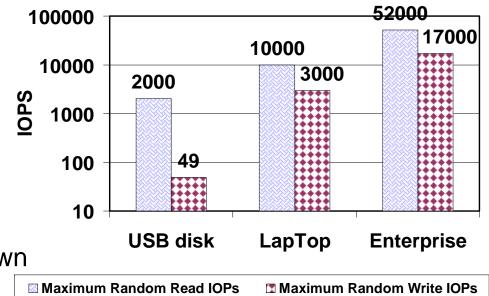

The cache/memory/storage hierarchy is rapidly becoming the **bottleneck for large systems**.

We know how to create MIPS & MFLOPS cheaply and in abundance,

but feeding them with data has become

the performance-limiting and most-expensive part of a system (in both \$ and Watts).

Data Center Infrastructure", John Humphreys, Jed Scaramella

system technology – "Storage Technologies & Systems" special issue of the IBM Journal of R&D (2008)

Jan 2013

#### ...yet critical applications are also undergoing a paradigm shift

Compute-centric paradigm

Main Focus:

Bottleneck:

Typical Examples:

Solve differential equations

CPU / Memory

Computational Fluid Dynamics Finite Element Analysis Multi-body Simulations

Extrapolation to 2020

(at 90% CGR → need **1.7 PB/sec**)

- 5.6 million HDD

- **19,000** sq. ft. !!

- 25 <u>Mega</u>watts

#### Analyze petabytes of data

Storage & I/O

Search and Mining Analyses of social/terrorist networks Sensor network processing Digital media creation/transmission Environmental & economic modeling

(at 90% CGR → need 8.4G SIO/sec)

- 21 million HDD

- **70,000** sq. ft. !!

- 93 <u>Mega</u>watts

[Freitas:2008]

3

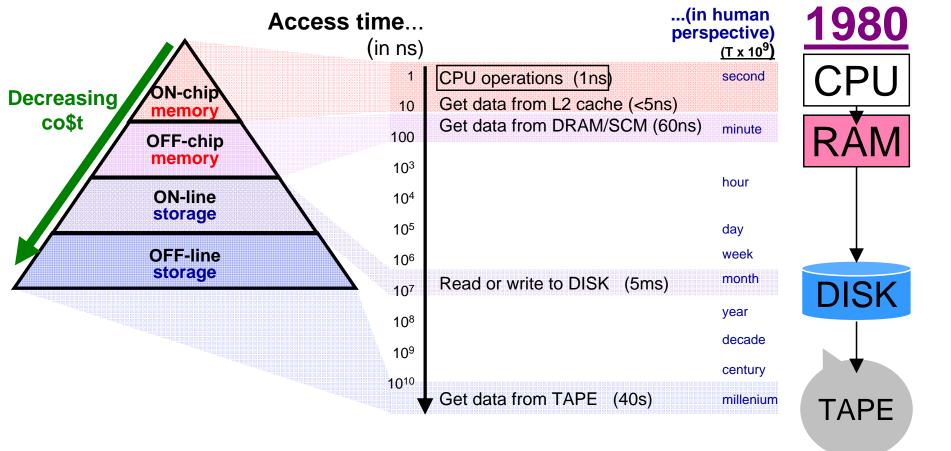

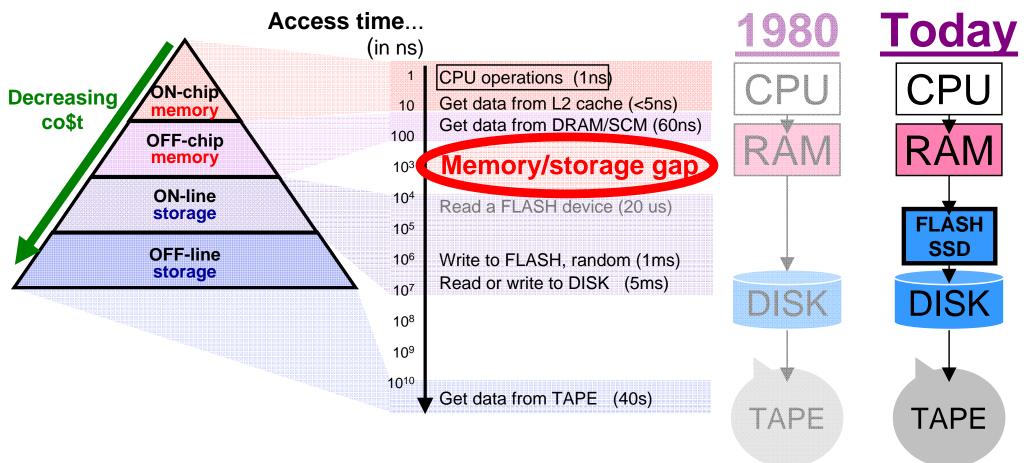

#### Problem (& opportunity): The access-time gap between memory & storage

- Modern computer systems have long had to be designed around hiding the access gap between memory and storage → caching, threads, predictive branching, etc.

- "Human perspective" if a CPU instruction is analogous to a 1-second decision by a human, retrieval of data from off-line tape represents an analogous delay of 1250 years

#### Problem (& opportunity): The access-time gap between memory & storage

• Today, **Solid-State Disks** based on NAND Flash can offer fast ON-line storage, and storage capacities are increasing as devices scale down to smaller dimensions...

...but while prices are dropping, the **performance gap** between memory and storage remains significant, and the already-**poor device endurance** of Flash is getting worse.

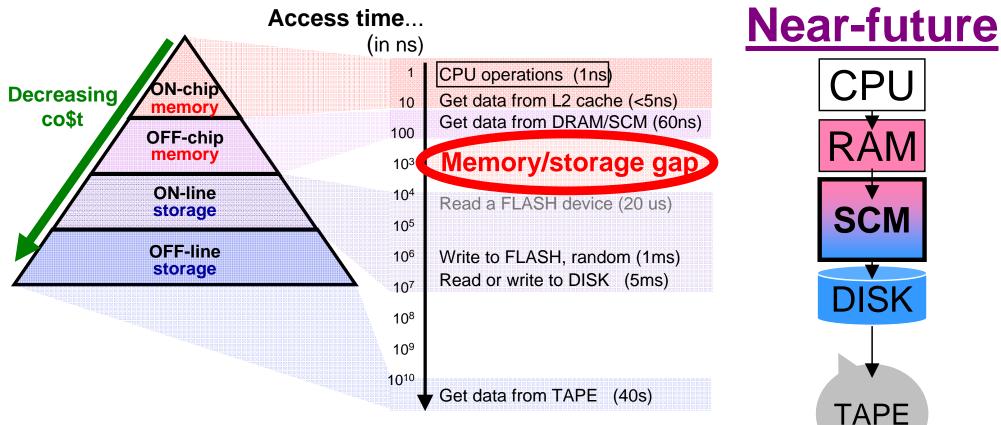

#### Problem (& opportunity): The access-time gap between memory & storage

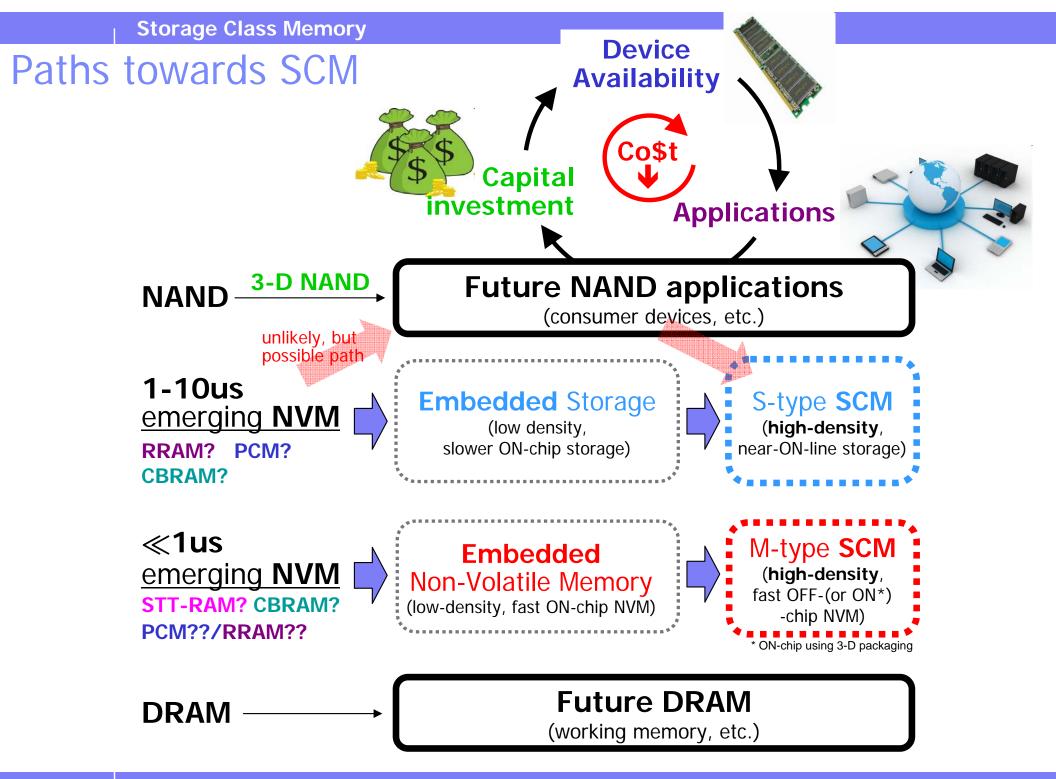

Research into new solid-state non-volatile memory candidates

- originally motivated by finding a "successor" for NAND Flash has opened up several interesting ways to change the memory/storage hierarchy...

- 1) **Embedded** Non-Volatile Memory low-density, fast ON-chip NVM

- 2) Embedded Storage low density, slower ON-chip storage

- 3) M-type Storage Class Memory high-density, fast OFF- (or ON\*)-chip NVM

- 4) S-type Storage Class Memory high-density, very-near-ON-line storage

\* ON-chip using 3-D packaging

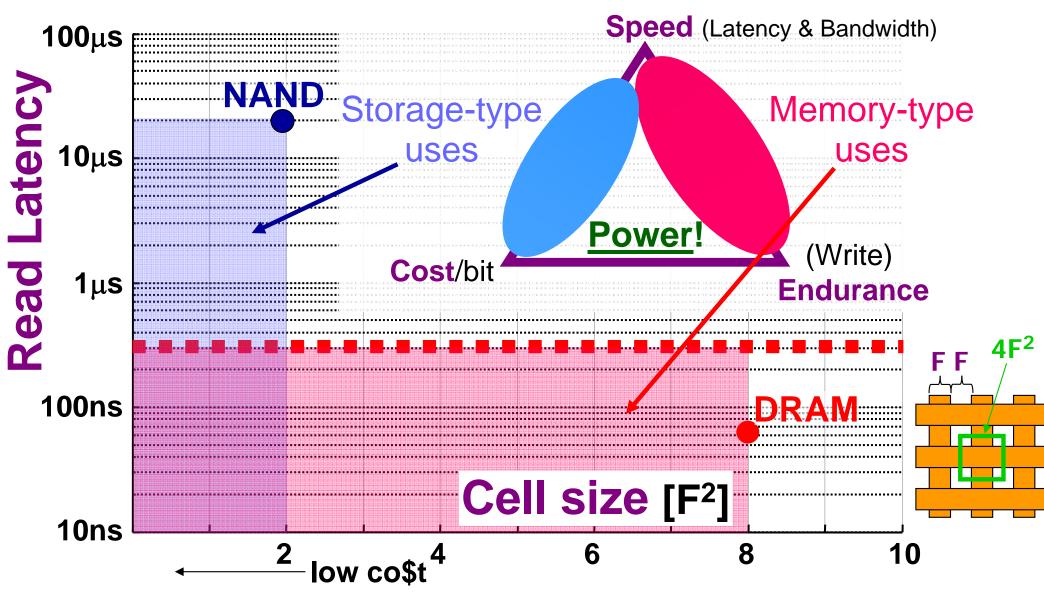

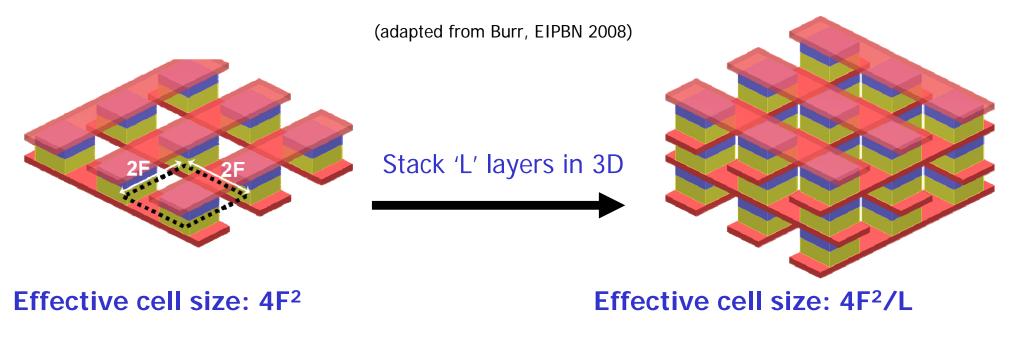

#### Storage-type vs. memory-type Storage Class Memory

The cost basis of semiconductor processing is well understood – the paths to higher density are 1) shrinking the minimum lithographic pitch **F**, and 2) storing **more bits PER 4F<sup>2</sup>**

7

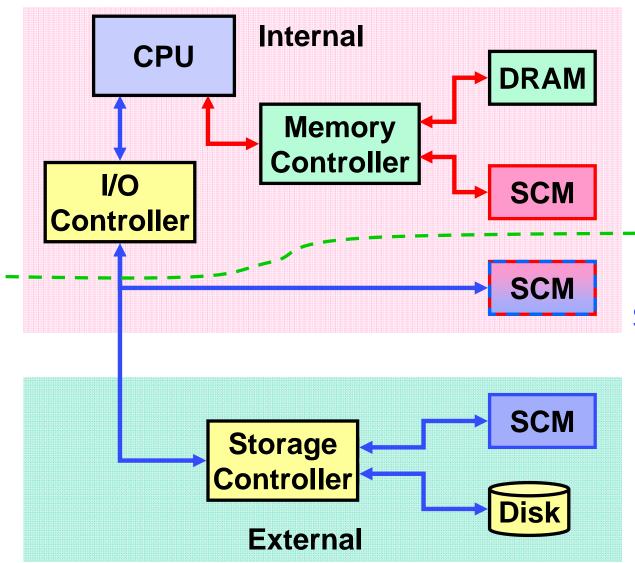

# S-type vs. M-type SCM

#### **M-type: Synchronous**

- Hardware managed

- Low overhead

- Processor waits

- New NVM → not Flash

- Cached or pooled memory

• Persistence (data survives despite component failure or loss of power) requires redundancy in system architecture

#### ~1us read latency ---

#### S-type: Asynchronous

- Software managed

- High overhead

- Processor doesn't wait, (process-, thread-switching)

- Flash or new NVM

- Paging or storage

- Persistence → RAID

## Competitive Outlook among emerging NVMs

(program code, etc.)

• **PCM** (but market disappearing)

**Embedded** Storage (low density, slower ON-chip storage)

- NAND? (but complicated process)

- RRAM?/PCM?

**Future NAND applications**

(consumer devices, etc.)

• **3-D NAND** (but crossover to succeed 20nm conventional NAND may require >50 layers!)

• PCM?/RRAM?

S-type Storage Class Memory (high-density, very-near-ON-line storage)

- 1) **PCM?/RRAM?**

- 2) Racetrack? (future?)

M-type Storage Class Memory (high-density, fast OFF- (or ON\*)-chip NVM)

- CBRAM? STT-RAM?

- PCM?/RRAM?

- Racetrack? (future?)

\* ON-chip using 3-D packaging

Embedded Non-Volatile Memory (low-density, fast ON-chip NVM)

STT-RAM? CBRAM?

Science & Technology – IBM Almaden Research Center

Low co\$t

High Speed

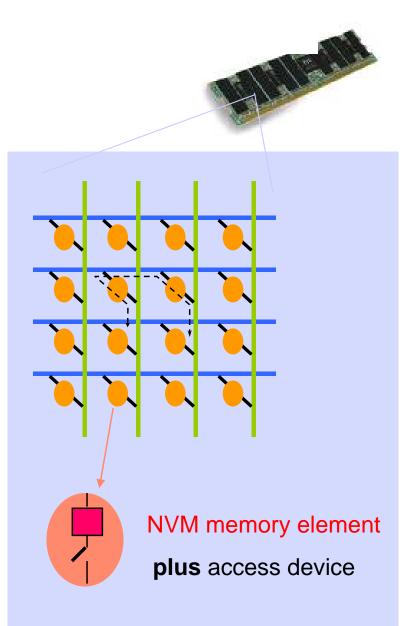

### NVM candidates for SCM

#### 1) NVM element

- Improved FLASH

- Magnetic Spin Torque Transfer

- → STT-RAM

- $\rightarrow$  Magnetic Racetrack

- Phase Change RAM

- Resistive RAM

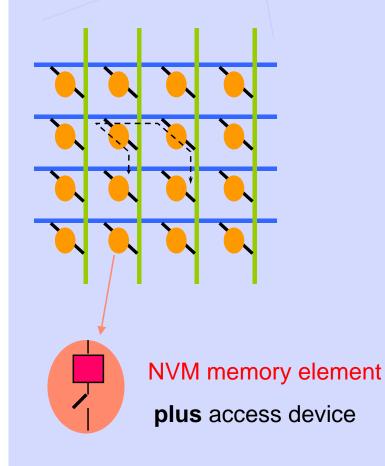

2) High-density access device (A.D.)

- 2-D silicon transistor or diode

- 3-D  $\rightarrow$  higher density per 4F<sup>2</sup>

- polysilicon diode (but <400°C processing?)

- MIEC A.D. (Mixed Ionic-Electronic Conduction)

- OTS A.D. (Ovonic Threshold Switch)

- Conductive oxide tunnel barrier A.D.

## **Generic SCM Array**

## Limitations of Flash

#### Asymmetric performance

Writes much slower than reads

#### Program/erase cycle

Block-based, no write-in-place

#### Data retention and Non-volatility

Retention gets worse as Flash scales down

#### Endurance

- Single level cell (SLC)  $\rightarrow$  10<sup>5</sup> writes/cell

- Multi level cell (MLC)  $\rightarrow 10^4$  writes/cell

- Triple level cell (TLC)  $\rightarrow$  ~300 writes/cell

#### Future outlook

- Scaling focussed solely on density

- 3-D schemes exist but are complex

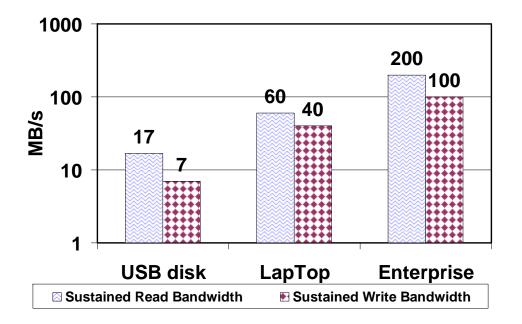

## STT (Spin-Torque-Transfer) RAM

• Controlled switching of free magnetic layer in a magnetic tunnel junction using current, leading to two distinct resistance states

#### Strengths

- Inherently very fast → almost as fast as DRAM

- Much better endurance than Flash or PCM

- Radiation-tolerant

- Materials are Back-End-Of-the-Line compatible

- Simple cell structure  $\rightarrow$  reduced processing costs

#### Weaknesses

- Achieving low switching current/power is not easy

- Resistance contrast is quite low (2-3x)  $\rightarrow$  achieving **tight distributions** is ultra-critical

- High-temperature retention strongly affected by scaling below F~50nm

- Tradeoff between fastest switching and switching reliability

**Outlook:** Strong outlook for an Embedded Non-Volatile Memory to replace/augment DRAM.

While near-term prospects for high-density SCM with STT-RAM may seem dim, **Racetrack Memory** offers hope for using STT concepts to create vertical "shift-register" of domain walls  $\rightarrow$  potential densities of 10-100 bits/F<sup>2</sup>

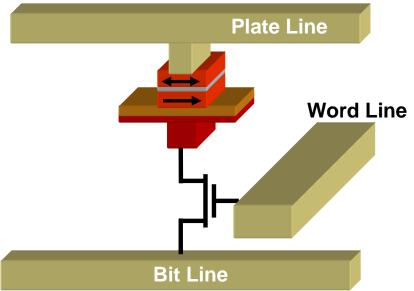

### Phase-change RAM

• Switching between **low-resistance** crystalline, and **high-resistance** amorphous phases, controlled through power & duration of electrical pulses

#### Strengths

- Very mature (large-scale demos & products)

- Industry consensus on material  $\rightarrow$  GeSbTe or GST

- Large resistance contrast  $\rightarrow$  analog states for  $\rm MLC$

- Offers much better endurance than Flash

- Shown to be highly scalable (still works at ultra-small F) and Back-End-Of-the-Line compatible

- Can be very fast (depending on material & doping)

#### Weaknesses

- RESET step to high resistance requires melting → power-hungry, thermal crosstalk? To keep switching power down → sub-lithographic feature and high-current Access Device To fill small feature → ALD or CVD → difficult now to replace GST with a better material Variability in small features broadens resistance distributions

- 10-year **retention at elevated temperatures** can be an issue → recrystallization

- Device characteristics change over time due to elemental segregation  $\rightarrow$  device failure

- MLC strongly affected by relaxation of amorphous phase  $\rightarrow$  "resistance drift"

- **Outlook:** NOR-replacement products now shipping  $\rightarrow$  if yield-learning successful and MLC drift-mitigation and/or 3-D Access Devices can offer high-density (=low-cost), then opportunity for NAND replacement, S-type, and then finally M-type SCM may follow

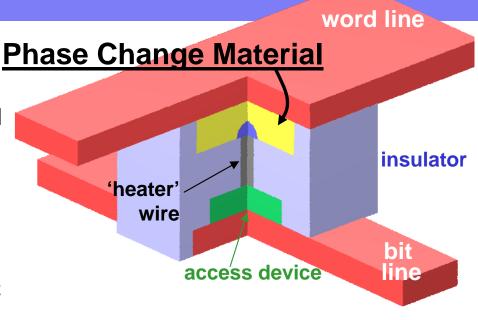

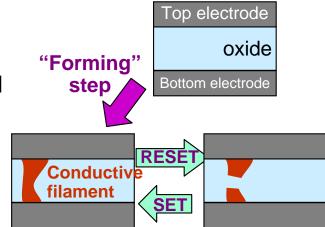

#### Resistive RAM Strengths

Voltage-controlled formation & dissipation of an oxygen-vacancy (or metallic) filament through an otherwise insulating layer

- Good retention at elevated-temperatures

- Simple cell structure  $\rightarrow$  reduced processing costs

- Both fast and ultra-low-current switching have been demonstrated

- Some RRAM materials are Back-End-Of-the-Line compatible

- Relatively new field  $\rightarrow$  high hopes for improved material concepts

- Less "gating" Intellectual Property to license

- Some RRAM concepts offer co-integrated NVM & Access Device

- Numerous ongoing development efforts

#### Weaknesses

- Highly immature technology wide variation in materials hampers cross-industry learning

- Demonstrated endurance is slightly better than Flash, but lower than PCM or STT-RAM

- Switching reliability an issue, even within single devices, and read disturb can be an issue

- An initial high-voltage "forming" step is often required

- To attain low RESET switching currents, circuit must constrain current during previous SET

- Unipolar and bipolar versions bipolar typically better in both write margins & endurance, but then requires an unconventional bipolar-capable Access Device (transistor or diode is out)

- High array yield with minimal "outlier" devices not yet demonstrated

- Tradeoff between switching speed, long-term retention, and reliability not yet explored

# Outlook: Outlook is unclear. Emergence of a strong material candidate offering high array yield & reliability could focus industry efforts considerably. Absent that, many uncertainties remain about prospects for reliable storage & memory products.

#### NVM candidates for SCM

- 1) NVM element

- Improved FLASH

- Magnetic Spin Torque Transfer

- → STT-RAM

- $\rightarrow$  Magnetic Racetrack

- Phase Change RAM

- Resistive RAM

#### 2) High-density access device (A.D.)

- 2-D silicon transistor or diode

- 3-D  $\rightarrow$  higher density per 4F<sup>2</sup>

- polysilicon diode (but <400°C processing?)

- MIEC A.D. (Mixed Ionic-Electronic Conduction)

- OTS A.D. (Ovonic Threshold Switch)

- Conductive oxide tunnel barrier A.D.

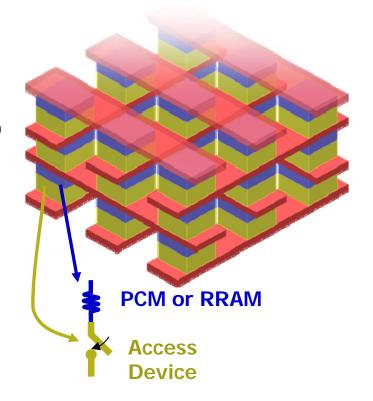

#### **Generic SCM Array**

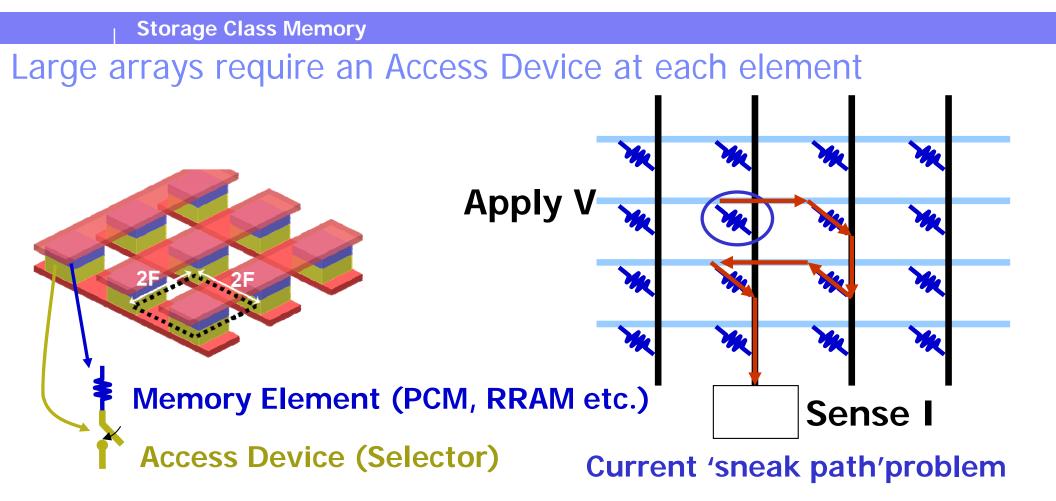

#### High density → 3D Multilayer Crosspoint Memory Array

As a result of the cost-basis of semiconductor manufacturing, memory cost is inversely related to bit density

F = minimum litho. feature size

Since they effectively Store more bits per 4F<sup>2</sup> footprint,

**3D** crosspoint arrays  $\Rightarrow$  a route to low cost memory

#### Access device needed in series with memory element

- Cut off current 'sneak paths' that lead to incorrect sensing and wasted power

- Typically diodes used as access devices

- Could also use devices with highly non-linear I-V curves

#### Requirements for an Access Device for 3D Crosspoint Memory

- High ON-state current density

>10 MA/cm<sup>2</sup> for PCM / RRAM RESET

- Low OFF-state leakage current >10<sup>7</sup> ON/OFF ratio, and wide low-leakage (< 100pA) voltage zone to accommodate half-selected cells in large arrays

- Back-End process compatible

<400C processing to allow 3D stacking</li>

- Bipolar operation needed for optimum RRAM operation

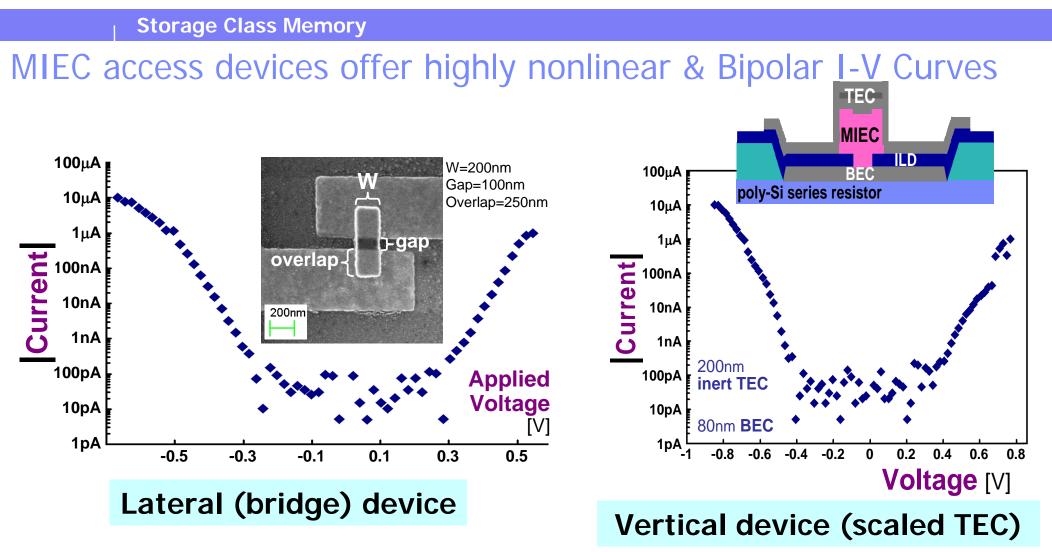

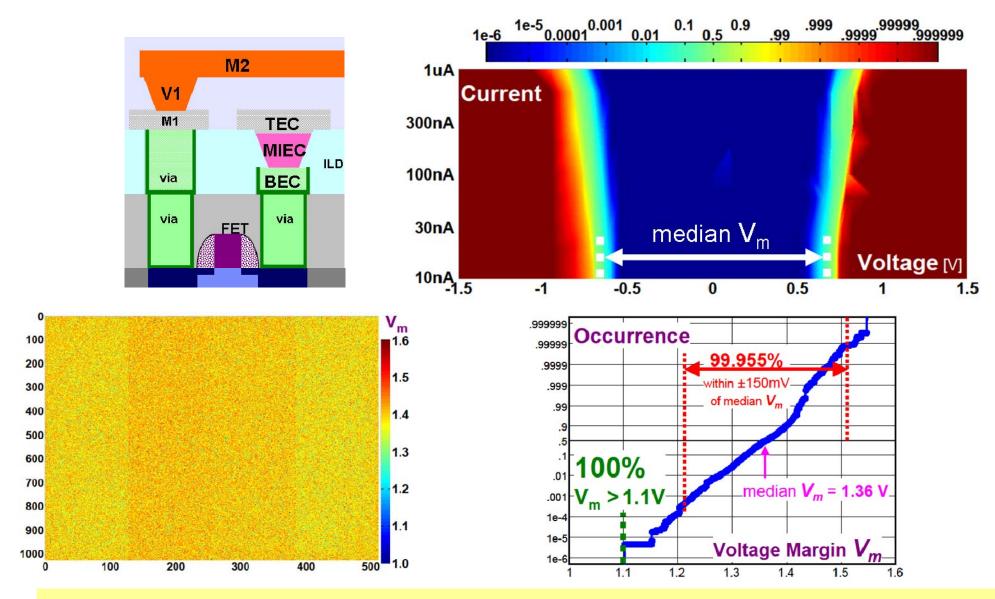

#### IBM's MIEC-based access device satisfies all these criteria

- Devices fabricated on 4inch wafers

- Voltage margin @ 10nA of 0.85V

- Suitable (desirable) for bipolar memory elements such as RRAM

#### **MIEC** access devices can operate in both polarities

(Gopalakrishnan *et al*, 2010 VLSI Tech. Sym.)

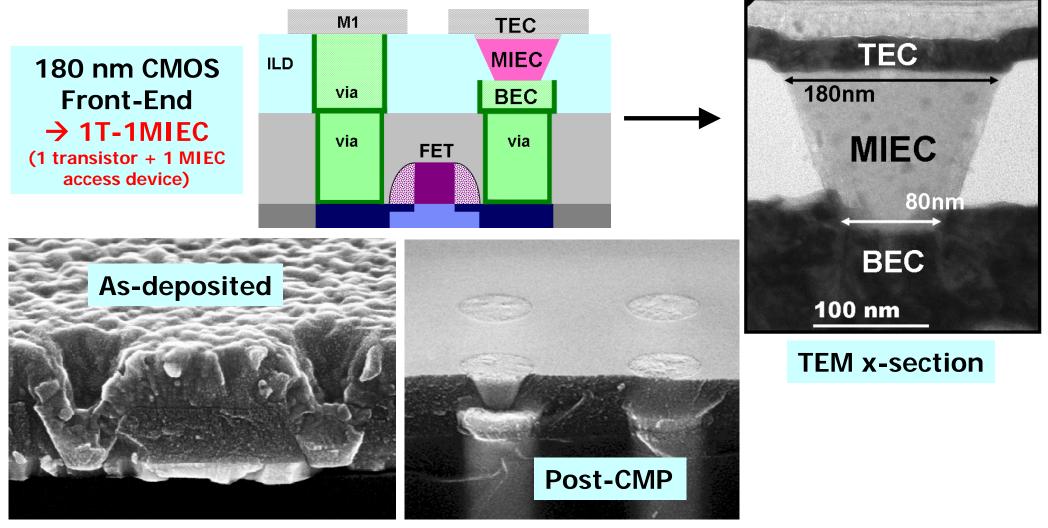

#### MIEC devices – 200mm wafer integration demonstrated

CMP process for MIEC material with modified commercial Cu slurry  $\rightarrow$

#### self-aligned MIEC Diode-in-Via (DIV) in a 200 mm wafer process

(Shenoy et al, 2011 VLSI Tech. Sym.)

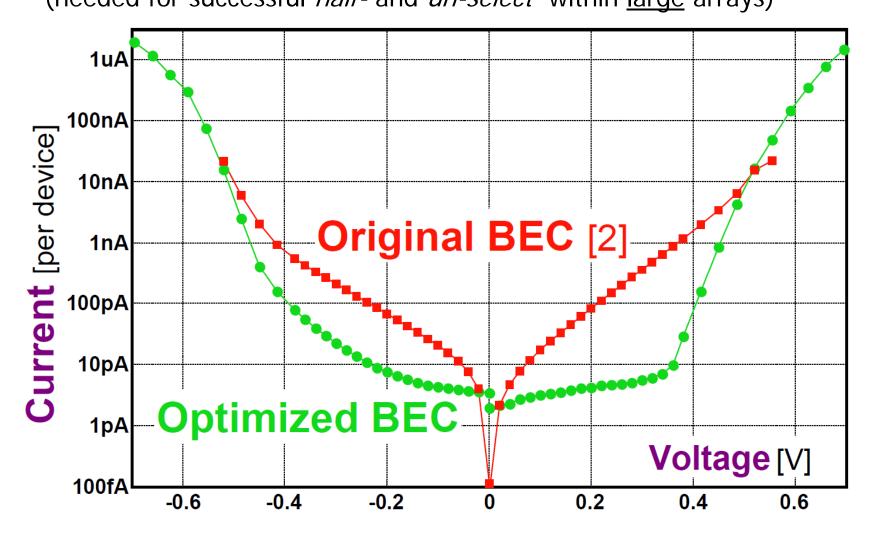

MIEC devices support ultra-low leakage currents (needed for successful *half-* and *un-select* within <u>large</u> arrays)

Voltage margin @ 10nA of 1.1V ~10 pA leakage currents near 0V & wide range with <100pA

(Burr et al, 2012 VLSI Tech. Sym.) (Shenoy et al, 2011 VLSI Tech. Sym.)

#### Large Arrays of MIEC have been integrated at 100% yield

#### 100% yield and tight distributions in 512 kbit 1T-1MIEC array

(Burr et al, 2012 VLSI Tech. Sym.)

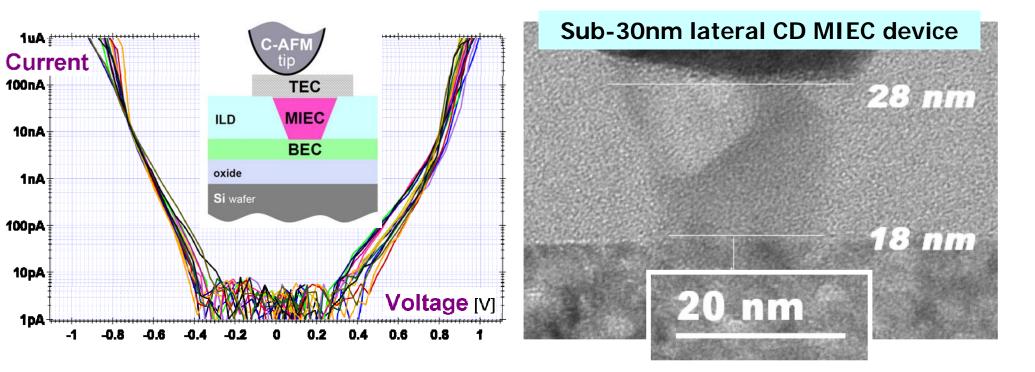

#### MIEC access devices are both fast and highly scalable

- High-current switching (RESET) of PCM demonstrated with 15ns pulses

- Low-current reads performed at << 1usec

- Devices retain low leakage characteristics down to <12nm thickness

- No lower limit to lateral CD scaling has been identified so far

(Virwani et al, 2012 IEDM)

#### Novel Mixed-Ionic-Electronic-Conduction (MIEC) Access Device

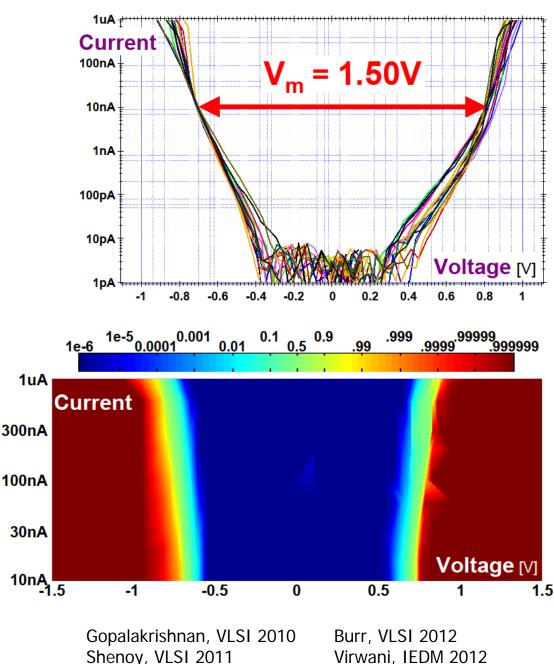

#### Strengths

- **High** enough **ON** currents for PCM cycling of PCM has been demonstrated

- Low enough OFF current for large arrays

- Very large (>>1e10) endurance for typical 5uA read currents

- Voltage margins > 1.5V with tight distributions  $\rightarrow$  sufficient for large arrays

- CMP process demonstrated

- 512kBit arrays demonstrated w/ 100% yield

- Scalable to <30nm CD, <12nm thickness

- Capable of 15ns write, <<1us read

#### Weaknesses

Maximum voltage across companion NVM during switching must be low (1-2V) → influences half-select condition and thus achievable array size

• Endurance during NVM programming is strongly dependent on programming current

#### What does the future hold?

- Consumer disk and enterprise tape will persist for the foreseeable future

- Flash will come into its own

- Flash may drive out enterprise disk, and if it doesn't, SCM will

- When will SCM arrive?

That will depend on the path the NAND industry takes after the 16-20nm node...

- <u>3-D NAND succeeds</u> → new NVMs (such as PCM, RRAM, STT-RAM) will develop slowly, driven only by SCM/embedded market

- <u>3-D NAND fails or is late</u> → one new NVM will be driven rapidly by NAND market

- If the latter, SCM could become the dominant storage technology by 2020

- The application software stack will be redesigned to utilize SCM-enabled persistent memory

#### For more information & acknowledgements

• K. Virwani, G. W. Burr, Rohit S. Shenoy, C. T. Rettner, A. Padilla, T. Topuria, P. M. Rice, G. Ho, R. S. King, K. Nguyen, A. N. Bowers, M. Jurich, M. BrightSky, E. A. Joseph, A. J. Kellock, N. Arellano, B. N. Kurdi and Kailash Gopalakrishnan, "Sub-30nm scaling and high-speed operation of fully-confined Access-Devices for 3-D crosspoint memory based on Mixed-Ionic-Electronic-Conduction (MIEC) Materials," *IEDM Technical Digest*, 2.7, (2012).

• Geoffrey W. Burr, Kumar Virwani, R. S. Shenoy, Alvaro Padilla, M. BrightSky, E. A. Joseph, M. Lofaro, A. J. Kellock, R. S. King, K. Nguyen, A. N. Bowers, M. Jurich, C. T. Rettner, B. Jackson, D. S. Bethune, R. M. Shelby, T. Topuria, N. Arellano, P. M. Rice, Bulent N. Kurdi, and K. Gopalakrishnan, "Large-scale (512kbit) integration of Multilayer-ready Access-Devices based on Mixed-Ionic-Electronic-Conduction (MIEC) at 100% yield," *Symposium on VLSI Technology*, T5.4, (2012).

• R. S. Shenoy, K. Gopalakrishnan, **Bryan Jackson**, K. Virwani, G. W. Burr, C. T. Rettner, A. Padilla, **Don S. Bethune**, R. M. Shelby, A. J. Kellock, M. Breitwisch, E. A. Joseph, R. Dasaka, R. S. King, K. Nguyen, A. N. Bowers, M. Jurich, A. M. Friz, T. Topuria, P. M. Rice, and B. N. Kurdi, "Endurance and Scaling Trends of Novel Access-Devices for Multi-Layer Crosspoint Memory based on Mixed Ionic Electronic Conduction (MIEC) Materials," *Symposium on VLSI Technology*, T5B-1, (2011).

• K. Gopalakrishnan, R. S. Shenoy, C. T. Rettner, K. Virwani, Don S. Bethune, R. M. Shelby, G. W. Burr, A. J. Kellock, R. S. King, K. Nguyen, A. N. Bowers, M. Jurich, B. Jackson, A. M. Friz, T. Topuria, P. M. Rice, and B. N. Kurdi, "Highly-Scalable Novel Access Device based on Mixed Ionic Electronic Conduction (MIEC) Materials for High Density Phase Change Memory (PCM) Arrays," *Symposium on VLSI Technology*, 19.4, (2010).

• G. W. Burr, Matt J. Breitwisch, Michele Franceschini, Davide Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, Luis A. Lastras, A. Padilla, Bipin Rajendran, S. Raoux, and R. Shenoy, "Phase change memory technology," *Journal of Vacuum Science & Technology B*, 28(2), 223-262, (2010).

• G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "An overview of candidate device technologies for Storage-Class Memory," *IBM Journal of Research and Development*, 52(4/5), 449 (2008).

• S. Raoux, G. W. Burr, M. J. Breitwisch, C. T. Rettner, Y. Chen, R. M. Shelby, M. Salinga, D. Krebs, S. Chen, H. L. Lung, and C. H. Lam, "Phase-change random access memory — a scalable technology," *IBM Journal of Research and Development*, **52**(4/5), 465,, (2008).

• Rich Freitas and Winfried Wilcke, "Storage Class Memory, the next storage system technology," *IBM Journal of Research and Development*, 52(4/5), 439, (2008).

• Yi-Chou Chen, Charlie T. Rettner, Simone Raoux, G. W. Burr, S. H. Chen, R. M. (Bob) Shelby, M. Salinga, W. P. Risk, T. D. Happ, G. M. McClelland, M. Breitwisch, A. Schrott, J. B. Philipp, M. H. Lee, R. Cheek, T. Nirschl, M. Lamorey, C. F. Chen, E. Joseph, S. Zaidi, B. Yee, H. L. Lung, R. Bergmann, and Chung Lam, "Ultra-Thin Phase-Change Bridge Memory Device Using GeSb," *IEDM Technical Digest*, paper S30P3, (2006).